Teledyne LeCroy TA700_800_850 User Manual User Manual

Page 249

APPENDIX C

Catalyst Enterprises, Inc.

235

Bus Protocol & Speed Sensing

Note:

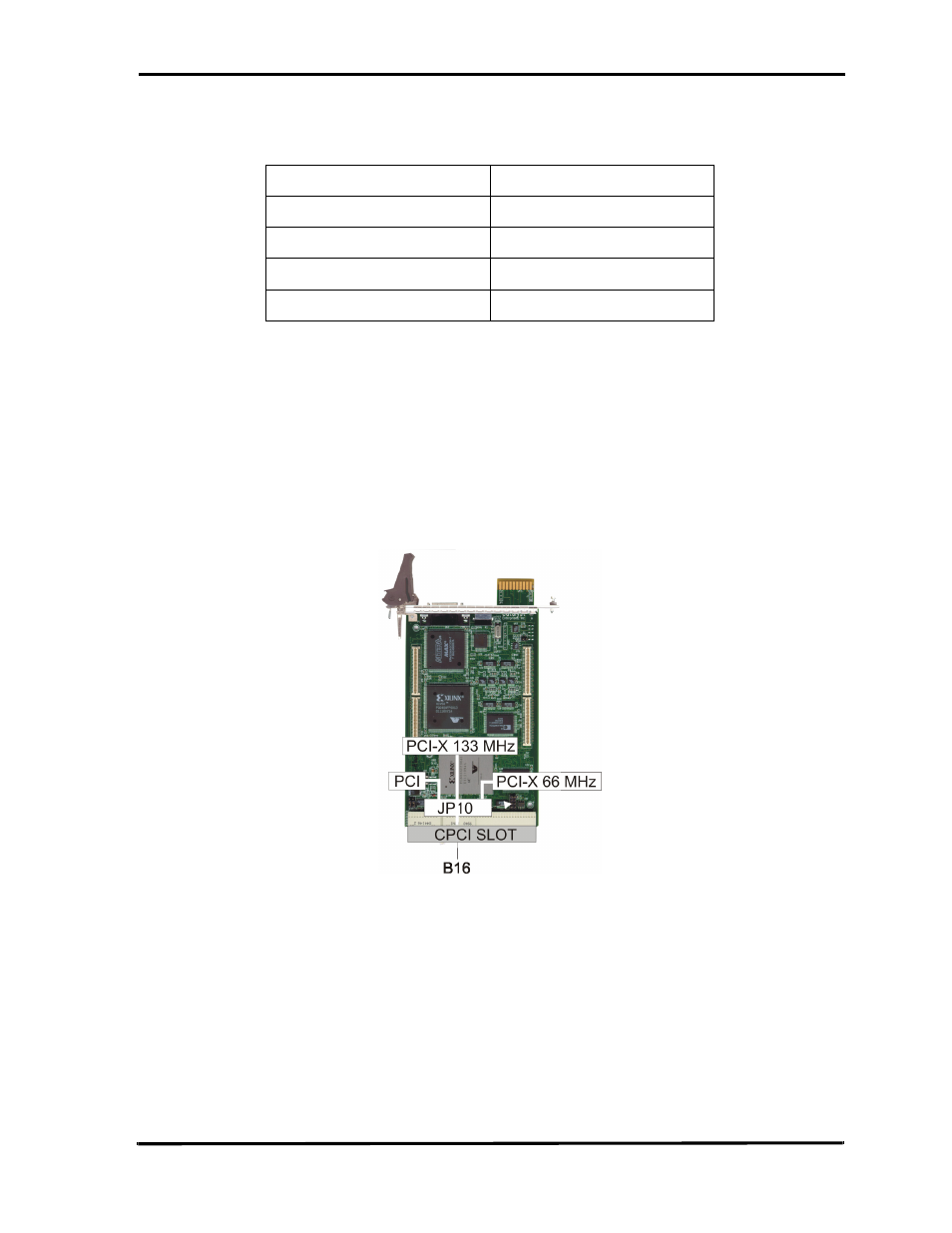

The JP10 jumper settings tell the central system arbiter the capability of the board.

The PCI and PCI-X bus speed and type is determined by the system BIOS at

powerup. During the time that RST# is asserted, the system reads the signals on D21

(M66EN) and B16 (PCIX CAP) from all of the boards asserted on the bus. At the

rising edge of RST# a message defining the bus protocol and operating speed that

satisfies the lowest performance on the bus is sent to all of the cards on the bus. This

message is sent by the following five control signals: FRAME, IRDY#, TRDY#,

DEVSEL# and STOP#.

Caution The JP10 setting information and the bus data returned at the rising edge of RST#

do not have to match if there is more than one agent on the bus.

JP10

Shunt 1-2 Top two

PCI-X 133MHz

Shunt 3-4 Next to top

N/A

Shunt 5-6 Next to bottom

PCI-X 66MHz

Shunt 7-8 Bottom two

PCI (Default)

- 6Zi Rackmount (12 pages)

- HDO Oscilloscope Rackmount (14 pages)

- LSIB-1 Host Interfaces (44 pages)

- OC1021 Oscilloscope Cart (9 pages)

- OC1024 Oscilloscope Cart (10 pages)

- OC910 Oscilloscope Cart (2 pages)

- TTL-AUX-OUT (1 page)

- WaveJet Rackmount (1 page)

- Zi Oscilloscope Rackmount (12 pages)

- USB2-GPIB (12 pages)

- WM8Zi-2X80GS (2 pages)

- WR6ZI-8CH-SYNCH (6 pages)

- Zi Oscilloscope Synchronization ProBus Module (Zi-8CH-SYNCH) (16 pages)

- LogicStudio (42 pages)

- WaveSurfer MXs-B Getting Started Manual (126 pages)

- WaveSurfer MXs-B Quick Reference Guide (16 pages)

- X-STREAM OSCILLOSCOPES Remote Control (305 pages)

- WS-GPIB (12 pages)

- PXA125 (219 pages)

- PXD Series (42 pages)

- PXD222 (38 pages)

- Oscilloscope System Recovery (8 pages)

- LabMaster 9Zi-A (264 pages)

- LabMaster 10Zi Rackmount (8 pages)

- LabMaster 10Zi Getting Started Manual (236 pages)

- LabMaster 10Zi Operators Manual (198 pages)

- WaveAce 1000_2000 (108 pages)

- WaveAce 1000_2000 Remote Control (92 pages)

- WaveRunner Xi-A Quick Reference Guide (16 pages)

- WaveRunner XI SERIES Operator’s Manual (233 pages)

- WaveMaster Automation Command (667 pages)

- WaveMaster 8 Zi_Zi-A (190 pages)

- WaveMaster 8000A (46 pages)

- WavePro 7 Zi_Zi-A (188 pages)

- WaveExpert series Automation Manual (285 pages)

- WaveExpert 9000_NRO9000_SDA100G Getting Started Manual (50 pages)

- WaveExpert 100H Operators Manual (348 pages)

- WaveRunner Automation Command (460 pages)

- WaveRunner Xi-A Getting Started Manual (128 pages)

- WaveRunner 6 Zi and 12-Bit HRO Getting Started Manual (198 pages)

- WaveRunner 6 Zi Quick Reference Guide (20 pages)

- WaveRunner 6 Zi-ExtRef-IN_OUT (2 pages)

- WaveSurfer Automation Command (226 pages)

- HDO 4000 Getting Started Guide (48 pages)

- HDO Removable Hard Drive (2 pages)