Teledyne LeCroy TA700_800_850 User Manual User Manual

Page 241

APPENDIX B

Catalyst Enterprises, Inc.

227

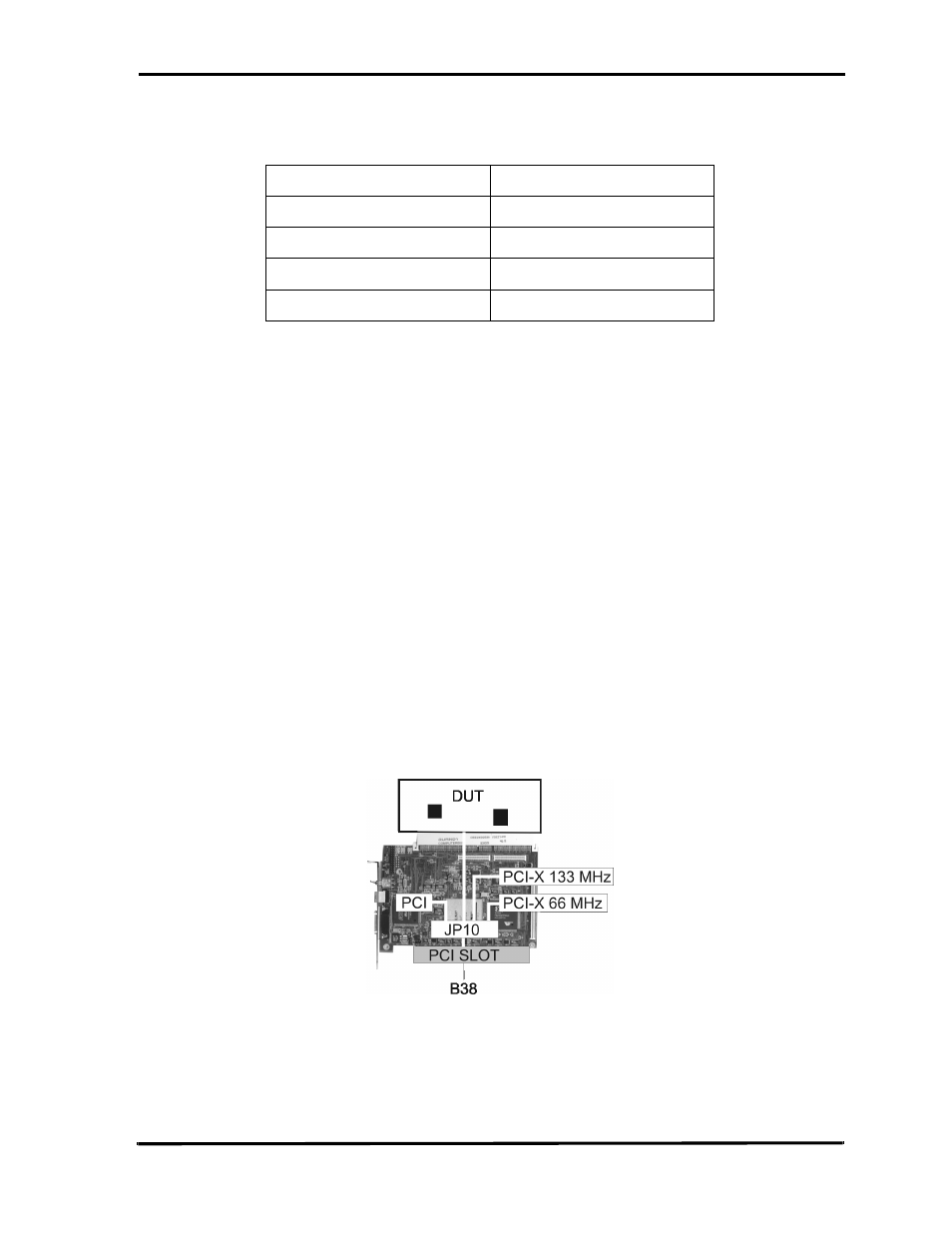

Bus Protocol & Speed Sensing

Note:

The JP10 jumper settings tell the central system arbiter what the capability of the

board. The PCI and PCI-X bus speed and type is determined by the system BIOS at

powerup. During the time that RST# is asserted, the system reads the signals on B49

(M66EN) and B38 (PCIXCAP) from all of the boards asserted on the bus. At the

rising edge of RST# a message defining the bus protocol and operating speed that

satisfies the lowest performance on the bus is sent to all of the cards on the bus. This

message is sent by the following five control signals: FRAME, IRDY#, TRDY#,

DEVSEL# and STOP#.

For example, if PCIX CAP is set to 0, the DUT is only PCI protocol capable and if

M66EN is 0, then the bus speed is PCI 33MHz and for M66EN = 1 the DUT is PCI

66MHz capable. For non zero values of PCIX CAP the bus speed is dependant on

the voltage level and can be either, PCIX 66MHz or PCIX 133 MHz.

Additionally the JP10 jumper setting allows the same bus information to be acquired

from the DUT during RST# or allow setting a predefined protocol and bus speed

regardless of the DUT capability

The bus information returned at the rising edge of RST# that must be decoded by

the DUT for proper information is also decoded by the TA700 and is displayed on

the bottom of the screen.

Caution The JP10 setting information and the bus data returned at the rising edge of RST#

do not have to match if there is more than one agent on the bus.

JP10

Shunt 1-2 Top two

PCI-X 133MHz

Shunt 3-4 Below top

DUT capabilities

Shunt 5-6 Next to bottom

PCI-X 66MHz

Shunt 7-8 Bottom two

PCI (Default)