Teledyne LeCroy TA700_800_850 User Manual User Manual

Page 175

Special Setups

Catalyst Enterprises, Inc.

161

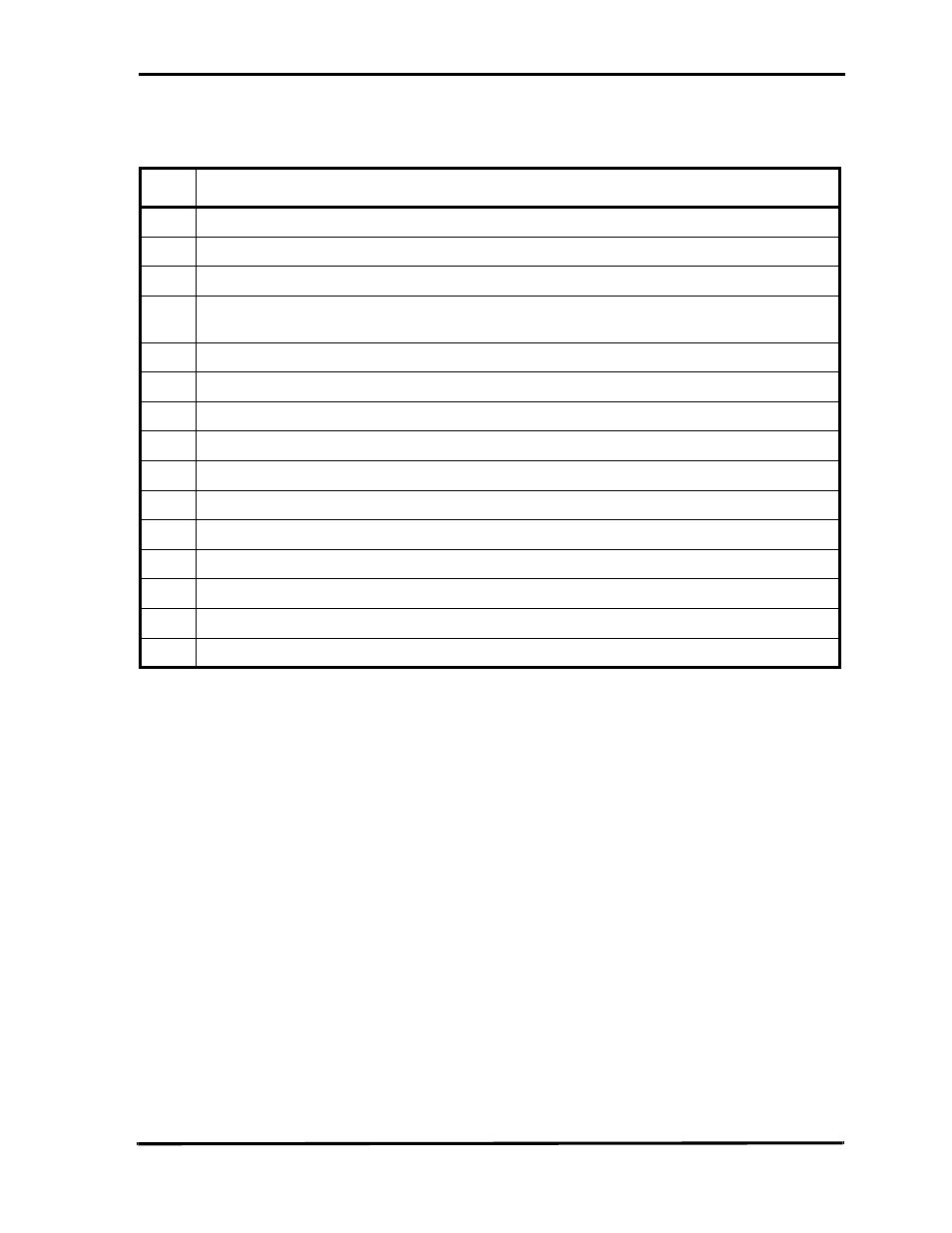

ERR44 Target has responded to a reserved command by asserting DEVSEL#. PCI-X Rev 1.0 - 2.4

ERR45 DEVSEL# was asserted during special cycle. PCI-X Rev 1.0 - 2.7.3

ERR46 FRAME# was asserted before the bus was granted (before GNT# was asserted). PCI-X Rev 1.0 - 1.10.2

ERR47 (*Overlapped Error*) IRDY# was asserted during the second address phase of a Dual Address Cycle. PCI-X Rev

1.0 - 2.12.1

ERR48 Reserved command was performed. PCI-X Rev 1.0 - 2.4

ERR49 PERR# was asserted during special cycle. PCI-X Rev 1.0 - 1.10.6

ERR50 PERR# was asserted during address cycle. PCI-X Rev 1.0 - 5

ERR51 PAR does not match parity across AD[31:0] and CBE[3:0] PCI-X Rev 1.0 - 5.3

ERR52 PAR64 does not match parity across AD[63:32] and CBE[7:4] PCI-X Rev 1.0 - 5.3

ERR53 Data parity error was detected on AD[31..0], but PERR# was not asserted. PCI-X Rev 1.0 - 1.10.6

ERR54 Data parity error was detected on AD[63..32], but PERR# was not asserted. PCI-X Rev 1.0 - 1.10.6

ERR55 REQ64# was not asserted during the same time as FRAME#. PCI-X Rev 1.0 - 2.12.3

ERR56 ACK64# was not asserted during the same time as DEVSEL#. PCI-X Rev 1.0 1.12.3

ERR57 ACK64# was asserted before REQ64# was asserted. PCI-X Rev 1.0 - 2.12.3

ERR58 Bus Command was not reflected on C/BE[7..4] during DAC transaction. PCI-X Rev 1.0 - 2.12.1

Table 4. PCI-X Protocol Errors (0-58)

Err. #

Description