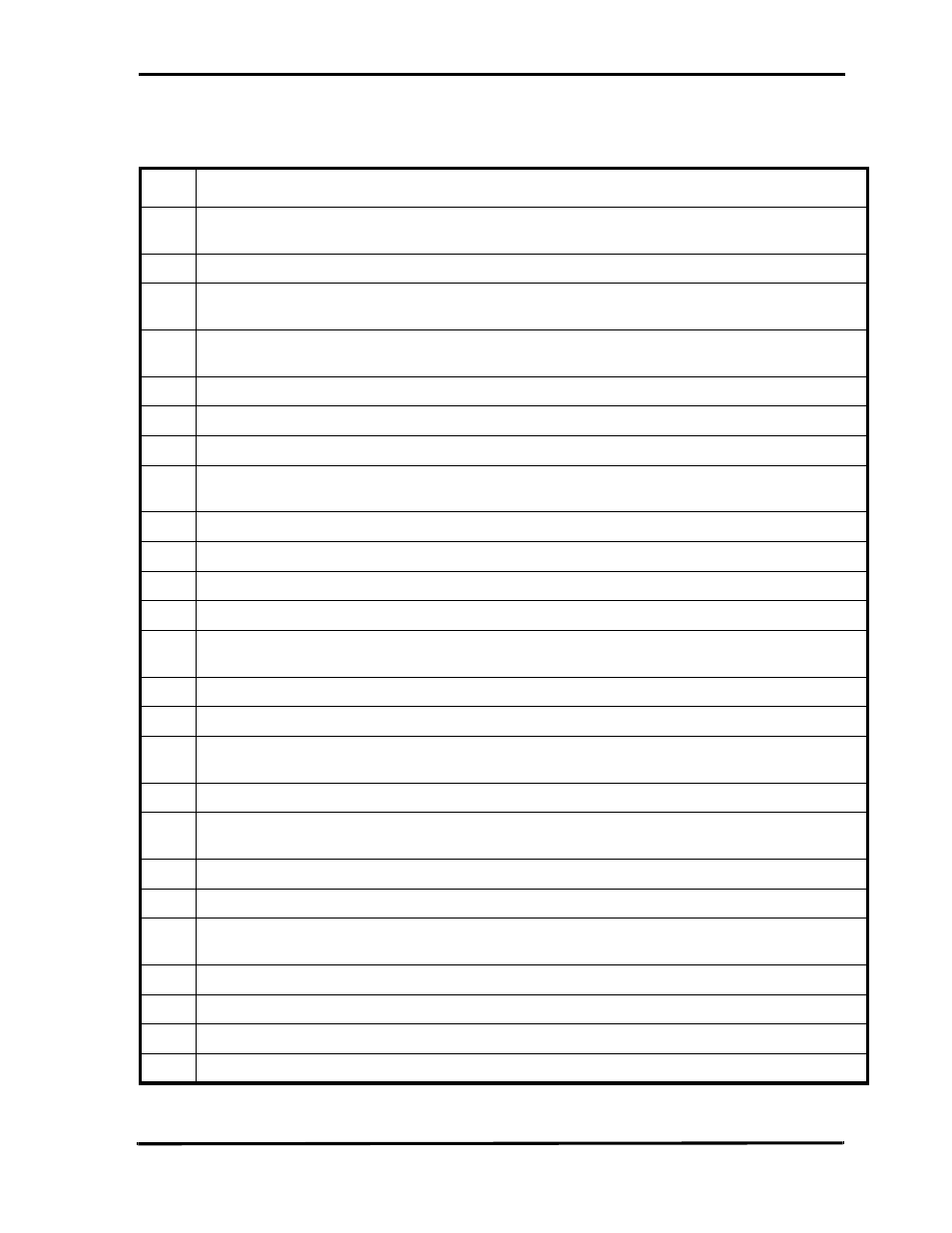

Table 3. pci protocol errors (0-51) – Teledyne LeCroy TA700_800_850 User Manual User Manual

Page 171

Special Setups

Catalyst Enterprises, Inc.

157

ERR24 Improper termination by Target. STOP# was asserted and de-asserted while FRAME# was still asserted. PCI Rev 2.2. -

3.3.2.1. Rule 4

ERR25 STOP# was asserted before DEVSEL# was asserted. Appendix C, Rule 14

ERR26 DEVSEL#, TRDY# or STOP# were changed before the current data phase was completed, after STOP# was asserted.

PCI Rev 2.2 - Appendix C, Rule 12 d

ERR27 Improper Back-to-Back transaction. Either DEVSEL#, TRDY#, or STOP# were not delayed and were asserted on the

first cycle of the Back-to-Back transaction. PCI Rev 2.2. - 3.4.2.

ERR28 The first transaction on the LOCK# was not a read transaction. PCI Rev 2.2. - Appendix F, F.1, Rule 2

ERR29 LOCK# was not released when Retry was requested by the Target. PCI Rev 2.2. - Appendix F, F.1, Rule 4

ERR30 LOCK# was not released after target abort. PCI Rev 2.2 - Appendix F, F.1, Rule 5

ERR31 LOCK# was not asserted the clock following the address phase or was not kept asserted throughout the transaction. PCI

Rev 2.2 - Appendix F, F.1, Rule 3

ERR32 REQ64# was not asserted during the same time as FRAME#. PCI Rev 2.2 - 3.8

ERR33 ACK64# was not asserted during the same time as DEVSEL#. PCI Rev 2.2 - 3.8

ERR34 REQ64# was asserted during a non-memory transaction. PCI Rev 2.2 - 3.8

ERR35 ACK64# was asserted before REQ64# was asserted. PCI Rev 2.2 - 3.8

ERR36 TRDY# is not asserted within 8 clocks on the data phase of the burst transfer. ERR36 applies only to second or

subsequent transfers, first transfer which is 16 clocks is covered by ERR37. PCI Rev 2.2 - 3.5.4.1

ERR37 TRDY# or STOP# not asserted within 16 clocks on the first data phase of the burst transfer. PCI Rev 2.2 - 3.5.4.1

ERR38 IRDY# was not asserted within 8 clocks from the time FRAME# was asserted. PCI Rev 2.2 - 3.5.4.1

ERR39 Master did not abort within 6 clocks from the time FRAME# was asserted while DEVSEL# was never asserted. PCI

Rev 2.2 - 3.5.4.1

ERR40 DEVSEL# asserted after 5 clocks from the time FRAME# was asserted. PCI Rev 2.2 - 3.5.4.1

ERR41 REQ# was not deasserted for a minimum of 2 clocks after a Retry and or a Disconnect by the Target. PCI Rev 2.2 -

Appendix C, Rule 10

ERR42 Target has not recognized configuration cycle type 00 or 01 and has asserted DEVSEL#. PCI Rev 2.2 - 3.2.2.3

ERR43 The IO byte address (AD0, AD1) given at the start of cycle does not match the CBE, byte enable. PCI Rev 2.2. - 3.2.2.1

ERR44 Memory Write and Invalidate Command were not implemented in Linear Incrementing Burst Mode. PCI Rev 2.2. -

3.2.2.2

ERR45 Target did not disconnect after the first phase of Reserved Burst Ordering in memory commands. PCI Rev 2.2 - 3.2.2.2

ERR46 Master abort was done prior to 4 clocks from the address phase. PCI Rev 2.2 - 3.3.3.1 and 3.9

ERR47 Reserved command was performed. PCI Rev 2.2 - 3.1.1

ERR48 A second DAC was performed immediately following a DAC. PCI Rev 2.2 - 3.9

Table 3. PCI Protocol Errors (0-51)

Err.#

Description