9 error count registers, 1 line code violation count register (lcvcr), Error count registers – Rainbow Electronics DS26519 User Manual

Page 77

DS26519 16-Port T1/E1/J1 Transceiver

77 of 310

9.9.9 Error

Count

Registers

The DS26519 contains four counters that are used to accumulate line coding errors, path errors, and

synchronization errors. Counter update options include one second boundaries, 42ms (T1 mode only), 62.5ms (E1

mode only) or manually. See the Error Counter Configuration Register (

). When updated automatically, the

user can use the interrupt from the timer to determine when to read these registers. All four counters will saturate at

their respective maximum counts and they will not roll over. (Note: Only the Line Code Violation Count Register

has the potential to overflow but the bit error would have to exceed 10E-2 before this would occur.)

The DS26519 can share the one-second timer from Port 1 across all ports. All DS26519 error/performance

counters can be configured to update on the shared one-second source or a separate manual update signal input.

See the

register for more information. By allowing multiple framer cores to synchronously latch their

counters, the host software can be streamlined to read and process performance information from multiple spans in

a more controlled manner.

9.9.9.1 Line Code Violation Count Register (LCVCR)

Either bipolar violations or code violations can be counted. Bipolar violations are defined as consecutive marks of

the same polarity. In T1 mode, if the B8ZS mode is set for the receive side, then B8ZS codewords are not counted

as BPVs. In E1 mode, if the HDB3 mode is set for the receive side, then HDB3 codewords are not counted as

BPVs. If

.0 is set, then the LVC counts code violations as defined in ITU-T O.161. Code violations are

defined as consecutive bipolar violations of the same polarity. In most applications, the framer should be

programmed to count BPVs when receiving AMI code and to count CVs when receiving B8ZS or HDB3 code. This

counter increments at all times and is not disabled by loss of sync conditions. The counter saturates at 65,535 and

will not rollover. The bit error rate on an E1 line would have to be greater than 10E-2 before the VCR would

saturate. See

for details of exactly what the LCVCRs count.

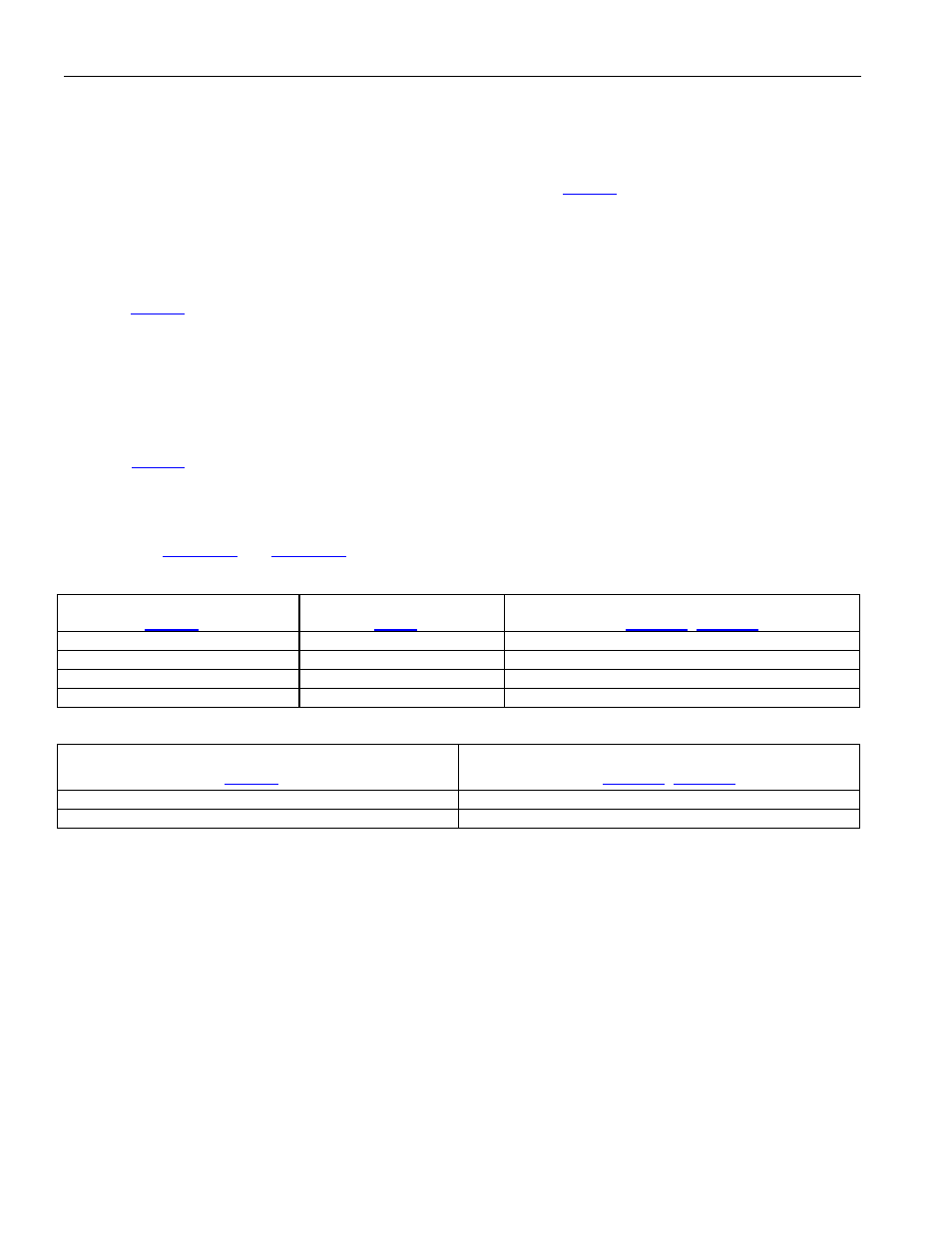

Table 9-28. T1 Line Code Violation Counting Options

COUNT EXCESSIVE ZEROS?

.0)

B8ZS ENABLED?

WHAT IS COUNTED

IN

,

No No

BPVs

Yes

No

BPVs + 16 consecutive zeros

No

Yes

BPVs (B8ZS/HDB3 codewords not counted)

Yes

Yes

BPVs + 8 consecutive zeros

Table 9-29. E1 Line Code Violation Counting Options

E1 CODE VIOLATION SELECT

WHAT IS COUNTED

IN

,

0 BPVs

1 CVs