Rainbow Electronics DS26519 User Manual

Page 272

DS26519 16-Port T1/E1/J1 Transceiver

272 of 310

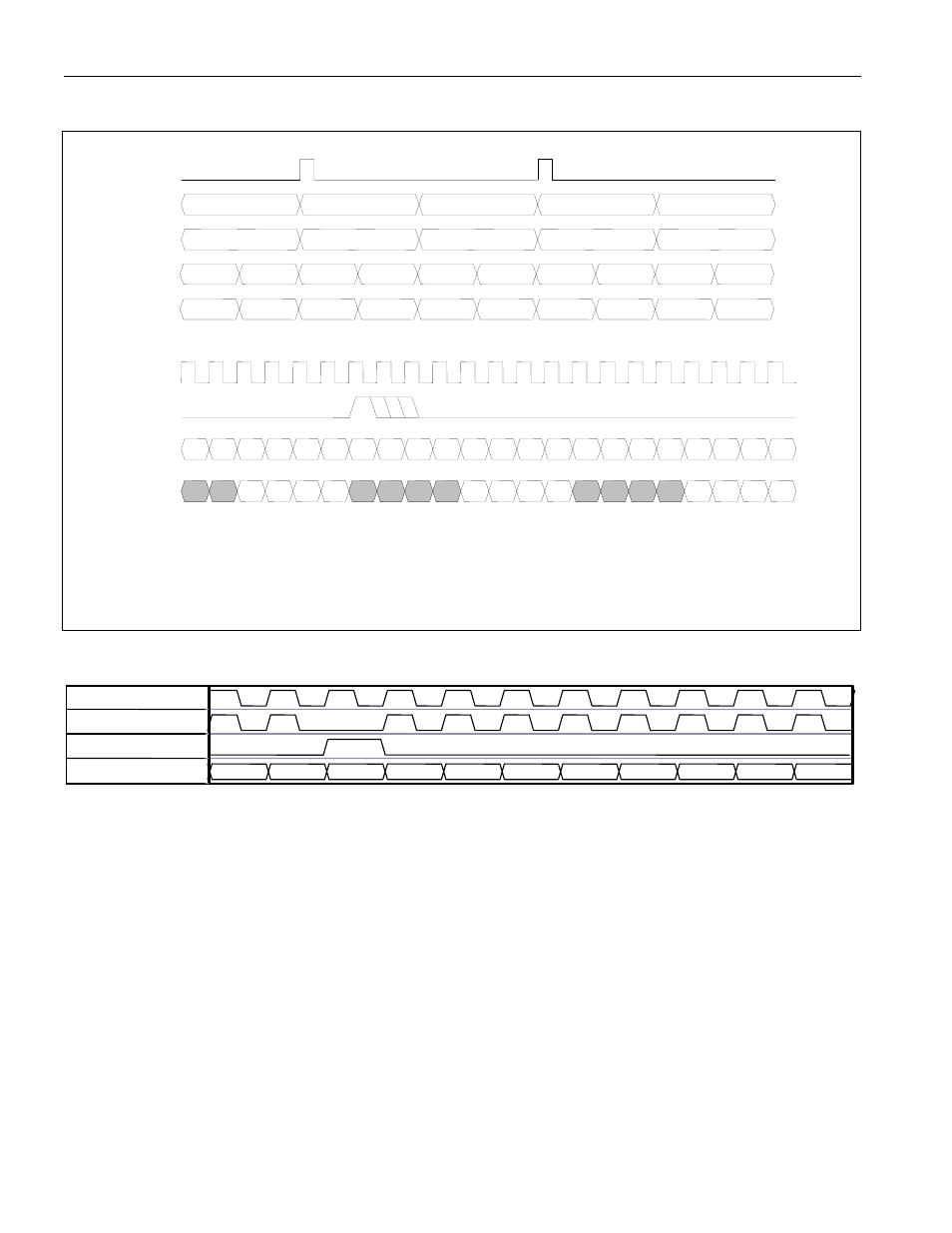

Figure 11-7. T1 Receive-Side Interleave Bus Operation—FRAME Mode

FR1 CH1-32

FR0 CH1-32

FR1 CH1-32

FR2 CH1-32

FR3 CH1-32

FR0 CH1-32

FR1 CH1-32 FR2 CH1-32 FR3 CH1-32 FR0 CH1-32 FR1 CH1-32 FR2 CH1-32

FR3 CH1-32

FR0 CH1-32

FR1 CH1-32

RSERn

LSB

RSYSCLKn

RSYNCn

FRAMER 3, CHANNEL 32

MSB

LSB

FRAMER 0, CHANNEL 1

RSIGn

FRAMER 3, CHANNEL 32

FRAMER 0, CHANNEL 1

MSB

LSB

FRAMER 0, CHANNEL 2

FRAMER 0, CHANNEL 2

RSERn

1

RSYNCn

RSIGn

1

RSERn

2

RSIGn

2

BIT DETAIL

A

B

C/A

D/B

A

B

C/A D/B

A

B

C/A

D/B

FR1 CH1-32

FR0 CH1-32

FR1 CH1-32

FR0 CH1-32

FR1 CH1-32

FR2 CH1-32

FR3 CH1-32

FR0 CH1-32

FR1 CH1-32 FR2 CH1-32 FR3 CH1-32 FR0 CH1-32 FR1 CH1-32 FR2 CH1-32

FR3 CH1-32

NOTE 1: 4.096MHz BUS CONFIGURATION.

NOTE 2: 8.192MHz BUS CONFIGURATION.

NOTE 3: RSYNCn IS IN THE INPUT MODE (RIOCR.2 = 0).

NOTE 4: SHOWS SYSTEM IMPLEMENATION WITH MULTIPLE DS26519 CORES DRIVING THE BACKPLANE.

NOTE 5: THOUGH NOT SHOWN, RCHCLKn CONTINUES TO MARK THE CHANNEL LSB FOR THE FRAMER'S ACTIVE PERIOD.

NOTE 6: THOUGH NOT SHOWN, RCHBLKn CONTINUES TO MARK THE BLOCKED CHANNELS FOR THE FRAMER’S ACTIVE PERIOD.

Figure 11-8. T1 Receive-Side RCHCLKn Gapped Mode During F-Bit

RCLKn

RCHCLKn

RSYNCn

RSERn

LSB

F-BIT

MSB