Tls1, 2) to kno, 3). th – Rainbow Electronics DS26519 User Manual

Page 239

DS26519 16-Port T1/E1/J1 Transceiver

239 of 310

Register Name:

TLS1

Register Description:

Transmit Latched Status Register 1

Register Address:

190h + (200h x (n - 1)) + (2000h x [(n - 1) / 8]): where n = 1 to 16

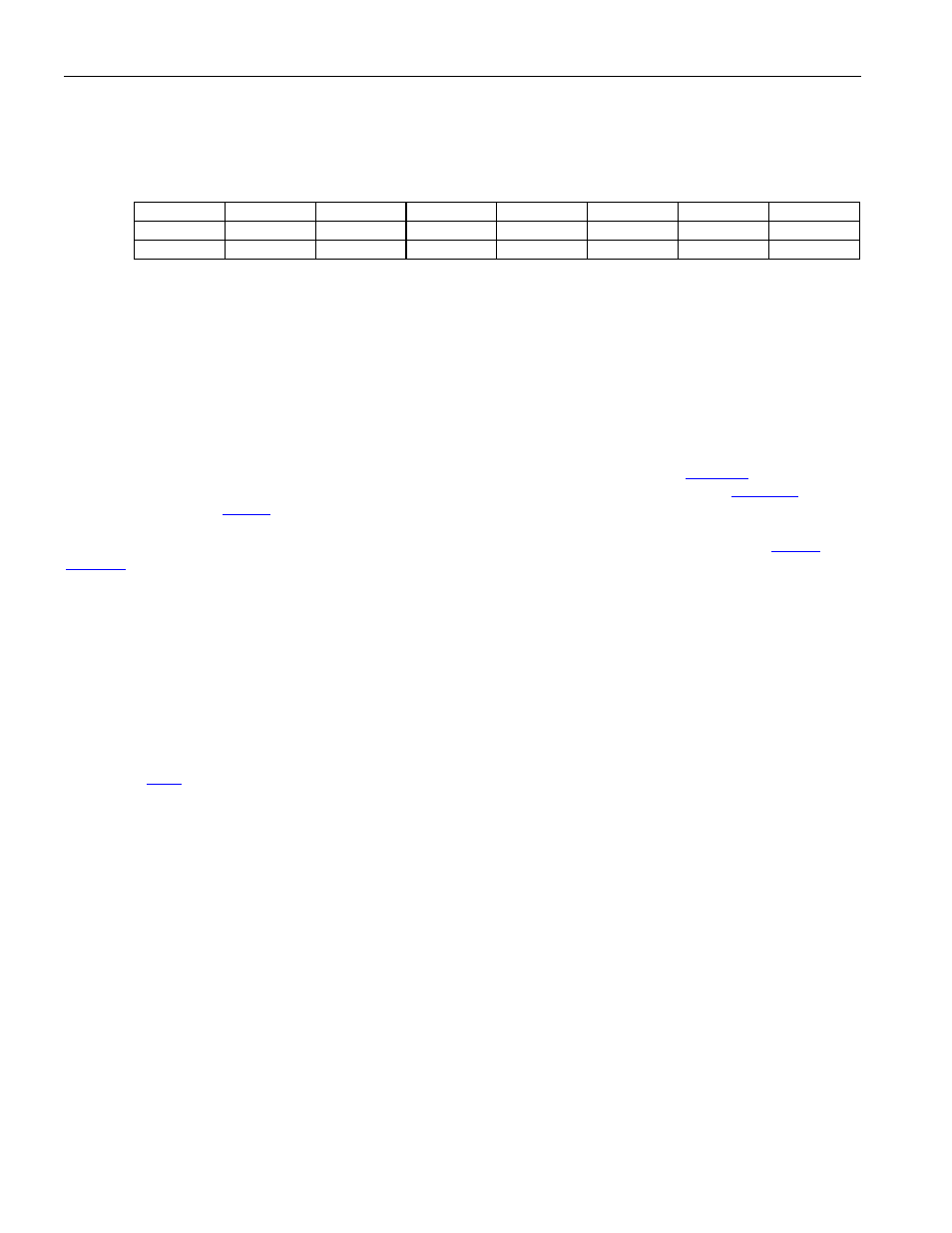

Bit

# 7 6 5 4 3 2 1 0

Name TESF

TESEM

TSLIP

TSLC96 —

TMF

LOTCC LOTC

TESF TESEM TSLIP

—

TAF TMF

LOTCC

LOTC

Default

0 0 0 0 0 0 0 0

Note: All bits in this register are latched and can cause interrupts.

Bit 7: Transmit Elastic Store Full Event (TESF). Set when the transmit elastic store buffer fills and a frame is

deleted.

Bit 6: Transmit Elastic Store Empty Event (TESEM). Set when the transmit elastic store buffer empties and a

frame is repeated.

Bit 5: Transmit Elastic Store Slip Occurrence Event (TSLIP). Set when the transmit elastic store has either

repeated or deleted a frame.

Bit 4: Transmit SLC-96 Multiframe Event (TSLC96) (T1 Mode Only). When enabled by

.6, this bit will

set once per SLC-96 multiframe (72 frames) to alert the host that new data may be written to the

–3

Bit 3: Transmit Align Frame Event (TAF) (E1 Mode Only). Set every 250

μs to alert the host that the

and

registers need to be updated.

Bit 2: Transmit Multiframe Event (TMF). In T1 mode, this bit is set every 1.5ms on D4 MF boundaries or every

3ms on ESF MF boundaries. In E1 operation, this but is set every 2ms (regardless if CRC-4 is enabled) on transmit

multiframe boundaries. Used to alert the host that signaling data needs to be updated.

Bit 1: Loss of Transmit Clock Condition Clear (LOTCC). Set when the LOTC condition has cleared (a clock has

been sensed at the TCLKn pin).

Bit 0: Loss of Transmit Clock Condition (LOTC). Set when the TCLKn pin has not transitioned for approximately

3 clock periods. Will force the LOTC pin high if enabled. This bit can be cleared by the host even if the condition is

still present. The LOTC pin will remain high while the condition exists, even if the host has cleared the status bit. If

enabled by

.0, the

INTB pin will transition low when this bit is set, and transition high when this bit is cleared (if

no other unmasked interrupt conditions exist).