Sters, Tcice1, Tjbe1 – Rainbow Electronics DS26519 User Manual

Page 219: Tjbe2, Tjbe3, Tjbe4, Tcice2, Tcice3, Tcice4

DS26519 16-Port T1/E1/J1 Transceiver

219 of 310

Register Name:

TCICE1, TCICE2, TCICE3, TCICE4

Register Description:

Transmit Channel Idle Code Enable Registers 1 to 4

Register Address:

150h, 151h, 152h, 153h + (200h x (n - 1)) + (2000h x [(n - 1) / 8]): where n = 1 to 16

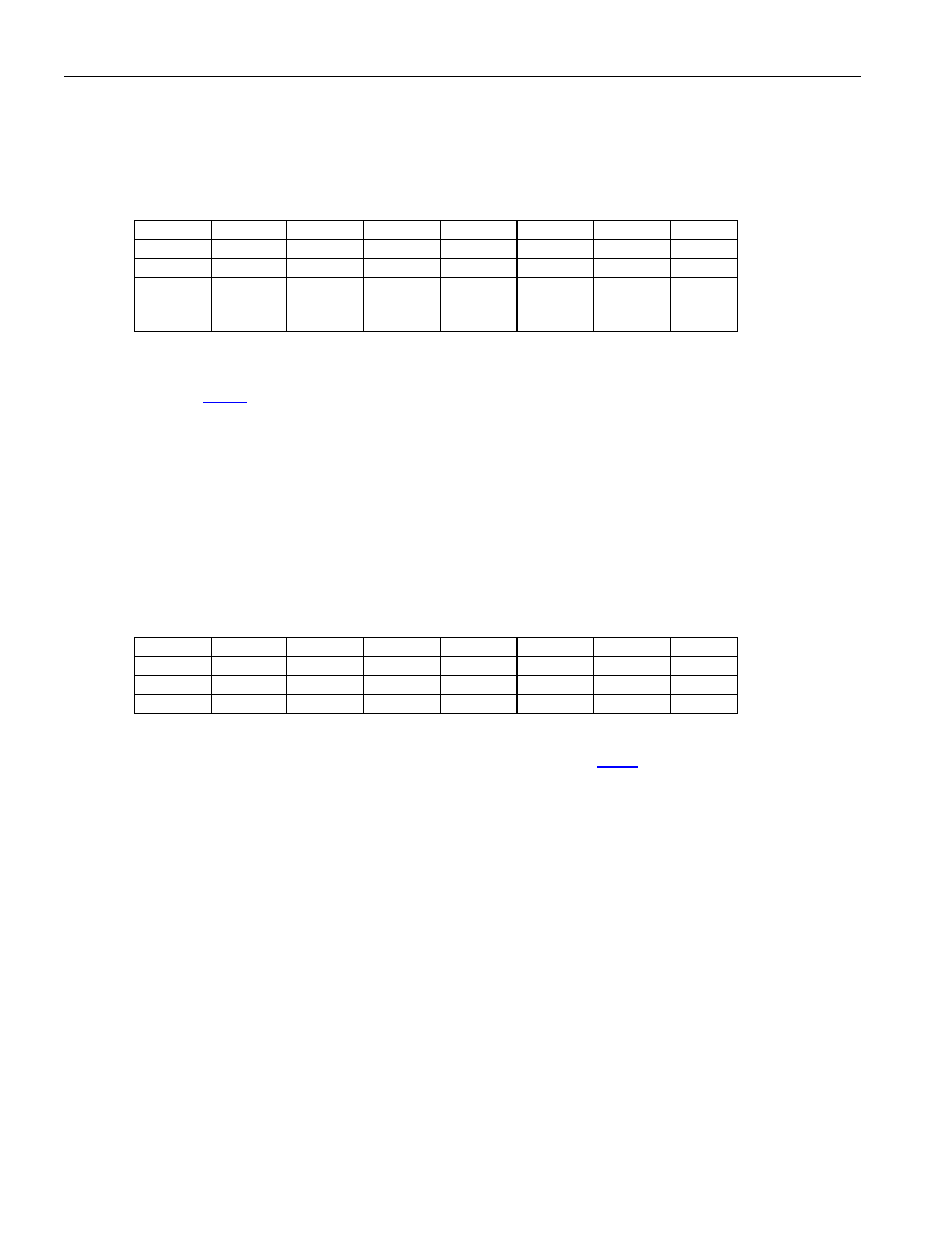

(MSB)

(LSB)

Bit

# 7 6 5 4 3 2 1 0

Name CH8 CH7 CH6 CH5 CH4 CH3 CH2 CH1

TCICE1

CH16 CH15 CH14 CH13 CH12 CH11 CH10 CH9

TCICE2

CH24 CH23 CH22 CH21 CH20 CH19 CH18 CH17

TCICE3

CH32 CH31 CH30 CH29 CH28 CH27 CH26 CH25

TCICE4

(E1 Mode

Only)

The Transmit Channel Idle Code Enable Registers (TCICE1–4) are used to determine which of the 24 T1 channels

(or 32 E1 channels) from the backplane should be overwritten with the code placed in the Transmit Idle Code

Definition Register (

–32).

Bits 7 to 0: Transmit Channels 1 to 32 Code Insertion Control Bits (CH[1:32])

0 = Do not insert data from the Idle Code Array into the transmit data stream.

1 = Insert data from the Idle Code Array into the transmit data stream.

Register Name:

TJBE1, TJBE2, TJBE3, TJBE4

Register Description:

Transmit Jammed Bit Eight Stuffing Registers 1 to 4

Register Address:

104h, 105h, 106h, 107h + (200h x (n - 1)) + (2000h x [(n - 1) / 8]): where n = 1 to 16

(MSB)

(LSB)

Bit

# 7 6 5 4 3 2 1 0

Name CH8 CH7 CH6 CH5 CH4 CH3 CH2 CH1

TJBE1

CH16 CH15 CH14 CH13 CH12 CH11 CH10 CH9

TJBE2

CH24 CH23 CH22 CH21 CH20 CH19 CH18 CH17

TJBE3

CH32 CH31 CH30 CH29 CH28 CH27 CH26 CH25

TJBE4

The Transmit Jammed Bit Eight Stuffing Registers (TJBE1–4) select which of the 24 T1 channels (or 32 E1

Channels) to insert jammed bit eight stuffing. These registers are enabled by

.TJBEN.

Bits 7 to 0: Transmit Channels 1 to 32 Jammed Bit Eight Stuffing Control Bits (CH[1:32])

0 = Do not affect data in this channel.

1 = Replace the channel with TJBES if the channel is all zeros.