Dram access cycle common characteristics, Dram random access cycle and dram fast-page cycle, Burst rom read cycle – Epson S1C33210 User Manual

Page 91: External bus master and nmi, Input, output and i/o port

8 ELECTRICAL CHARACTERISTICS

S1C33210 PRODUCT PART

EPSON

A-77

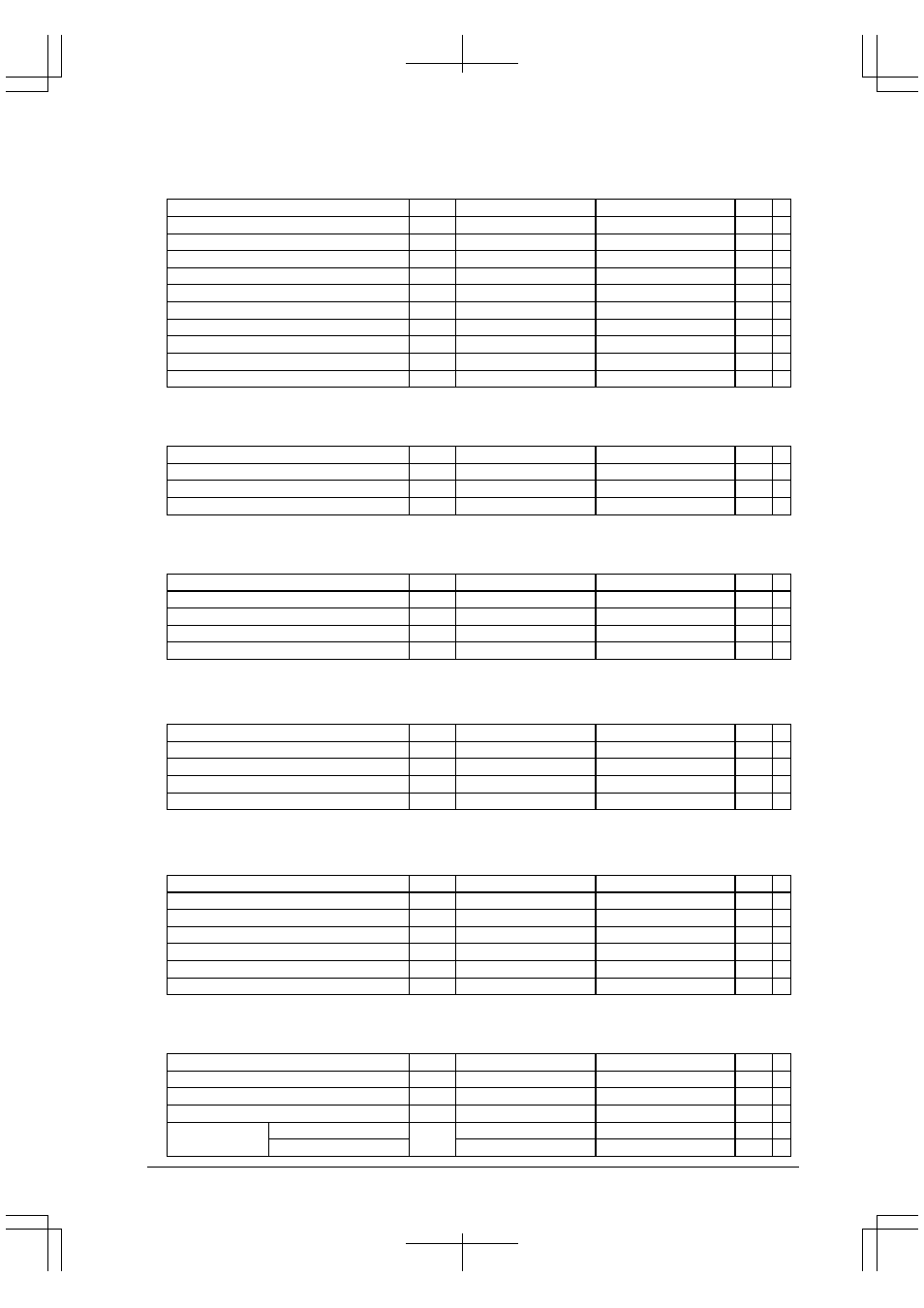

DRAM access cycle common characteristics

(Unless otherwise specified: V

DD

=2.7V to 3.6V, V

SS

=0V, Ta=-40

°

C to +85

°

C)

Item

Symbol

Min.

Max.

Unit

∗

#RAS signal delay time (1)

t

RASD1

10

ns

#RAS signal delay time (2)

t

RASD2

10

ns

#RAS signal pulse width

t

RASW

t

CYC

(2+WC)-10

ns

#CAS signal delay time (1)

t

CASD1

10

ns

#CAS signal delay time (2)

t

CASD2

10

ns

#CAS signal pulse width

t

CASW

t

CYC

(0.5+WC)-10

ns

Read signal delay time (3)

t

RDD3

10

ns

Read signal pulse width (2)

t

RDW2

t

CYC

(2+WC)-10

ns

Write signal delay time (3)

t

WRD3

10

ns

Write signal pulse width (2)

t

WRW2

t

CYC

(2+WC)-10

ns

DRAM random access cycle and DRAM fast-page cycle

(Unless otherwise specified: V

DD

=2.7V to 3.6V, V

SS

=0V, Ta=-40

°

C to +85

°

C)

Item

Symbol

Min.

Max.

Unit

∗

Column address access time

t

ACCF

t

CYC

(1+WC)-25

ns

#RAS access time

t

RACF

t

CYC

(1.5+WC)-25

ns

#CAS access time

t

CACF

t

CYC

(0.5+WC)-25

ns

EDO DRAM random access cycle and EDO DRAM page cycle

(Unless otherwise specified: V

DD

=2.7V to 3.6V, V

SS

=0V, Ta=-40

°

C to +85

°

C)

Item

Symbol

Min.

Max.

Unit

∗

Column address access time

t

ACCE

t

CYC

(1.5+WC)-25

ns

#RAS access time

t

RACE

t

CYC

(2+WC)-25

ns

#CAS access time

t

CACE

t

CYC

(1+WC)-20

ns

Read data setup time

t

RDS2

20

ns

Burst ROM read cycle

(Unless otherwise specified: V

DD

=2.7V to 3.6V, V

SS

=0V, Ta=-40

°

C to +85

°

C)

Item

Symbol

Min.

Max.

Unit

∗

Read address access time (2)

t

ACC2

t

CYC

(1+WC)-25

ns

Chip enable access time (2)

t

CEAC2

t

CYC

(1+WC)-25

ns

Read signal access time (2)

t

RDAC2

t

CYC

(0.5+WC)-25

ns

Burst address access time

t

ACCB

t

CYC

(1+WC)-25

ns

External bus master and NMI

(Unless otherwise specified: V

DD

=2.7V to 3.6V, V

SS

=0V, Ta=-40

°

C to +85

°

C)

Item

Symbol

Min.

Max.

Unit

∗

#BUSREQ signal setup time

t

BRQS

16

ns

#BUSREQ signal hold time

t

BRQH

0

ns

#BUSACK signal output delay time

t

BAKD

10

ns

High-impedance

→

output delay time

t

Z2E

10

ns

Output

→

high-impedance delay time

t

B2Z

10

ns

#NMI pulse width

t

NMIW

30

ns

Input, Output and I/O port

(Unless otherwise specified: V

DD

=2.7V to 3.6V, V

SS

=0V, Ta=-40

°

C to +85

°

C)

Item

Symbol

Min.

Max.

Unit

∗

Input data setup time

t

INPS

20

ns

Input data hold time

t

INPH

10

ns

Output data delay time

t

OUTD

20

ns

K-port interrupt

SLEEP, HALT2 mode

t

KINW

30

ns

input pulse width Others

2

×

t

CYC

ns