A.3 rom and burst rom, Burst rom and mask rom interface setup examples, Burst rom and mask rom interface timing – Epson S1C33210 User Manual

Page 114

APPENDIX A

A-100

EPSON

S1C33210 PRODUCT PART

A.3 ROM and Burst ROM

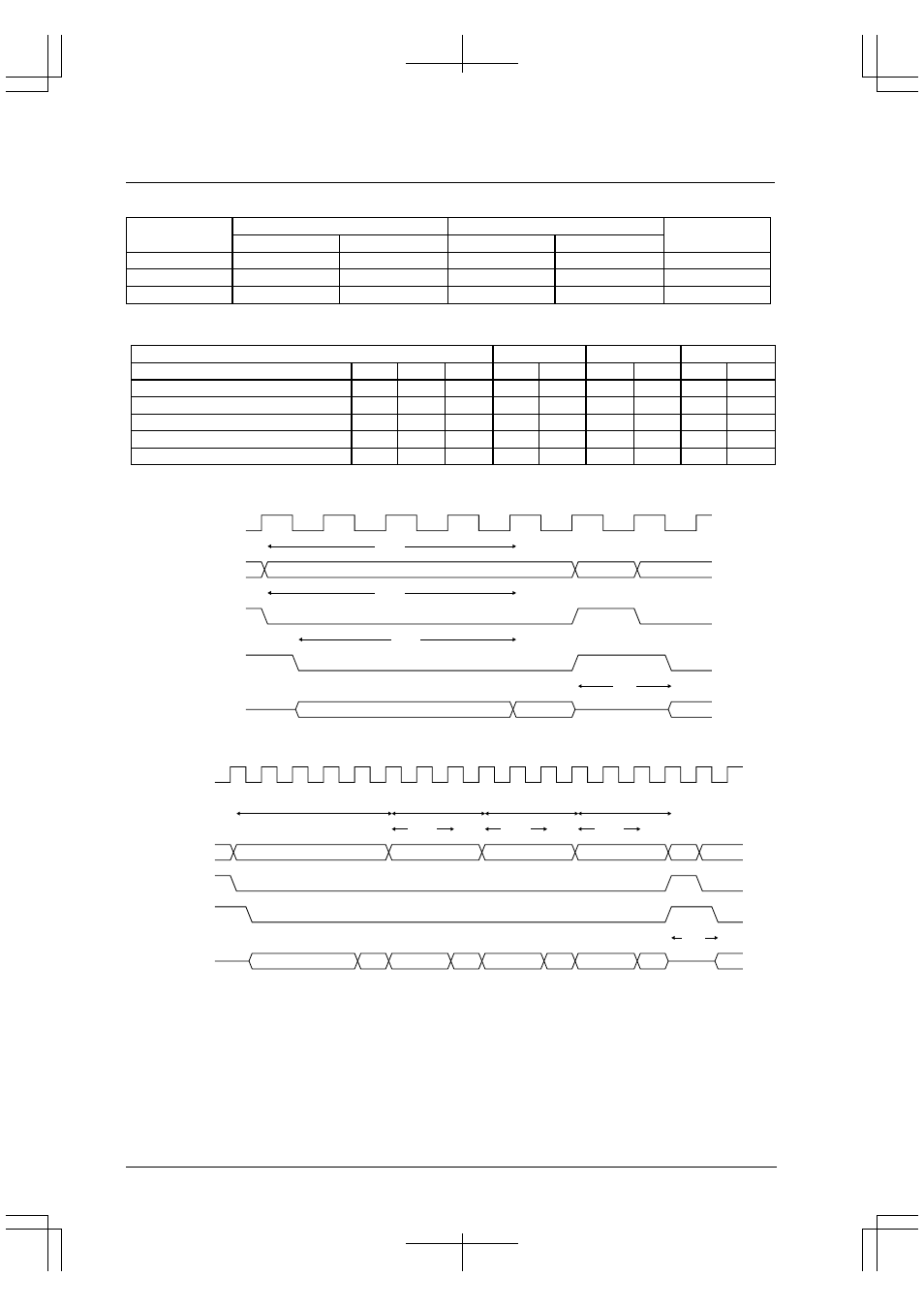

Burst ROM and mask ROM interface setup examples

Operating

Normal read cycle

Burst read cycle

Output disable

frequency

Wait cycle

Read cycle

Wait cycle

Read cycle

delay cycle

20MHz

2

3

1

2

1.5

25MHz

3

4

1

2

1.5

33MHz

4

5

2

3

1.5

Burst ROM and mask ROM interface timing

Burst ROM and mask ROM interface

33MHz

25MHz

20MHz

Parameter

Symbol

Min.

Max.

Cycle

Time

Cycle

Time

Cycle

Time

Access time

t

ACC

–

100

5

150

4

160

3

150

#CE output delay time

t

CE

–

100

5

150

4

160

3

150

#OE output delay time

t

OE

–

50

4.5

135

3.5

140

2.5

125

Burst access time

t

BAC

–

50

3

90

2

80

2

100

Output disable delay time

t

DF

0

40

1.5

45

1.5

60

1.5

75

ROM: 100ns, CPU: 33MHz, normal read

t

ACC

t

CE

t

OE

BCLK

A[23:0]

#CE9, 10

#RD

D[15:0]

RD data

;;;;;

;;;;;

;;;;;;;;;;;;;;;

;;;;;;;;;;;;;;;

;;;;

;;;;

t

DF

ROM: 100ns, CPU: 33MHz, burst read

Normal read cycle

Burst read cycle

t

BAC

t

BAC

t

BAC

BCLK

A[23:0]

#CE9, 10

#RD

D[15:0]

RD data

;;;

;;;

;;;;;;;;

;;;;;;;;

;;;

;;;

RD data

;;;;;

;;;;;

RD data

;;;;;

;;;;;

RD data

;;;;;

;;;;;

t

DF