Iii-10 monitored mobile access interfaces, Configuration of mobile access interfaces – Epson S1C33210 User Manual

Page 387

III PERIPHERAL BLOCK: MONITORED MOBILE ACCESS INTERFACES

S1C33210 FUNCTION PART

EPSON

B-III-10-1

III-10 Monitored Mobile Access Interfaces

Configuration of Mobile Access Interfaces

Features

The C33 peripheral block includes mobile access interfaces with the following features. Used in combination with

the software modem module, they support data communications with PDC, packet PDC, PHS, and CdmaOne

mobile devices.

•

There are four configuration choices.

PDC communications mode

ARQ frame processing for high-speed communications mode

HDLC communications mode

HDLC (packet) frame processing

PHS communications mode

PIAFS frame processing for beara transfers at 32 kbps or 64 kbps

UART communications mode

UART communications using serial interface Ch. 3

•

A serial-to-parallel converter with built-in buffer for communications data and CRC generator/checker handles

data conversion, data transfers, and synchronization detection for the interfaces.

•

The interfaces share I/O pins, whose configuration is switched between communications modes.

•

The built-in data buffer uses asynchronous dual-port RAM (1R/1W type) with a capacity of 96 16-bit words.

•

The module generates the following eight interrupt requests, mapped according to the communications mode

under program control to five interrupt request lines to the CPU core: PDC interrupt, HDLC receive interrupt,

HDLC transmit interrupt, HDLC Sp interrupt, HDLC E/S interrupt, PHS receive interrupt, PHS transmit

interrupt, and modem status change interrupt.

•

The module also includes some functions for controlling mobile access interface I/O ports.

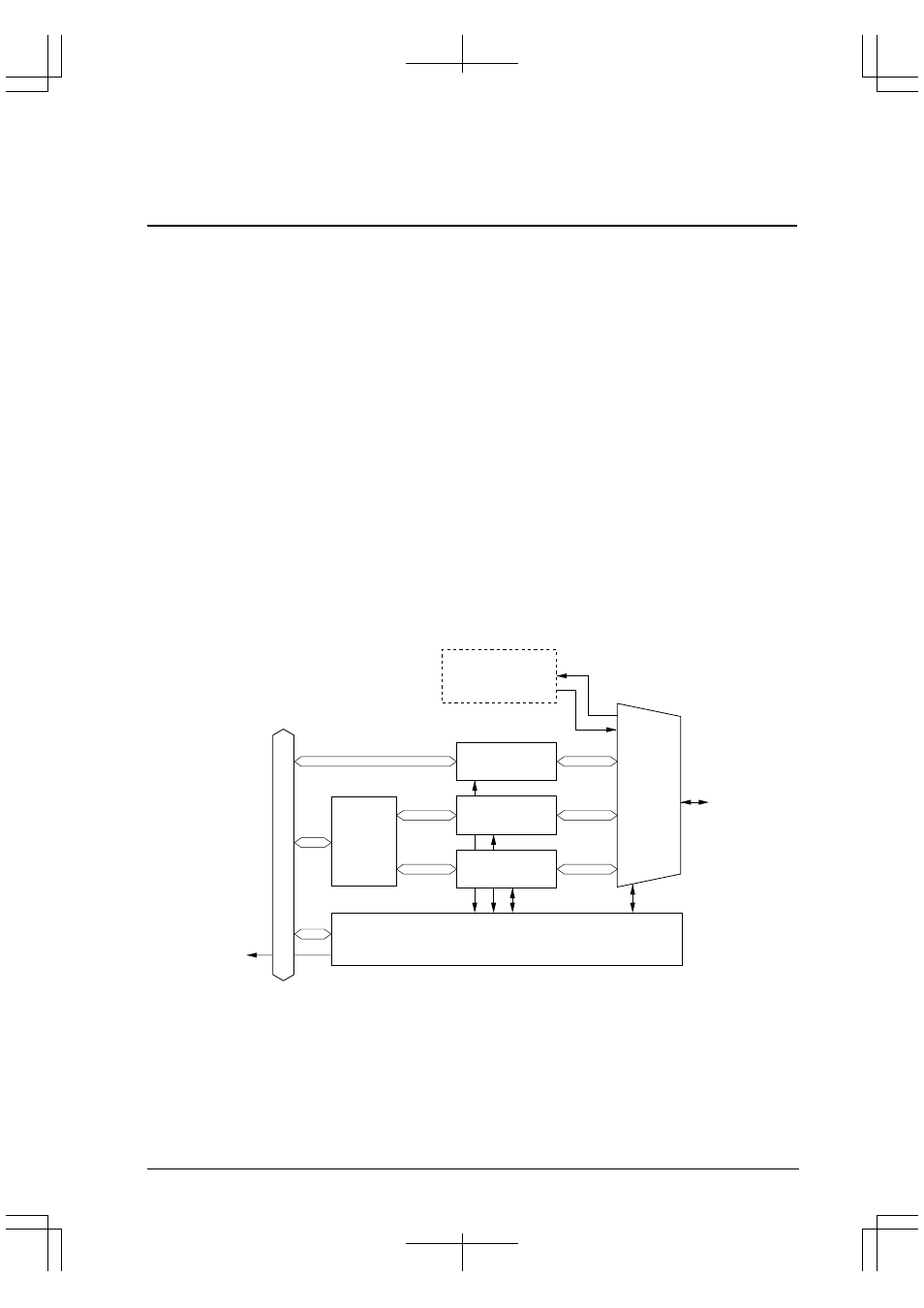

Figure 10.1 summarizes the mobile access interface components.

Serial interface Ch. 3

SIN3

SOUT3

Packet processor

(HDLC interface)

PDC processor

(PDC interface)

PIAFS processor

(PHS interface)

Communications

mode switch

Mobile access

interface I/O

Interrupt requests

System control block

Data

buffer

Inter

nal data b

u

s

System control block:

PIAFS processor:

PDC processor:

Packet processor:

Data buffer:

This switches the communications mode, controls I/O ports, etc.

This exchanges PIAFS frames with a PHS device.

This exchanges ARQ frames with a PDC device.

This exchanges HDLC frames with a PDC device supporting packets.

This holds data for frame data transfers.

Figure 10.1 Mobile Access Interface Components