I/o memory for mobile access interfaces – Epson S1C33210 User Manual

Page 407

III PERIPHERAL BLOCK: MONITORED MOBILE ACCESS INTERFACES

S1C33210 FUNCTION PART

EPSON

B-III-10-21

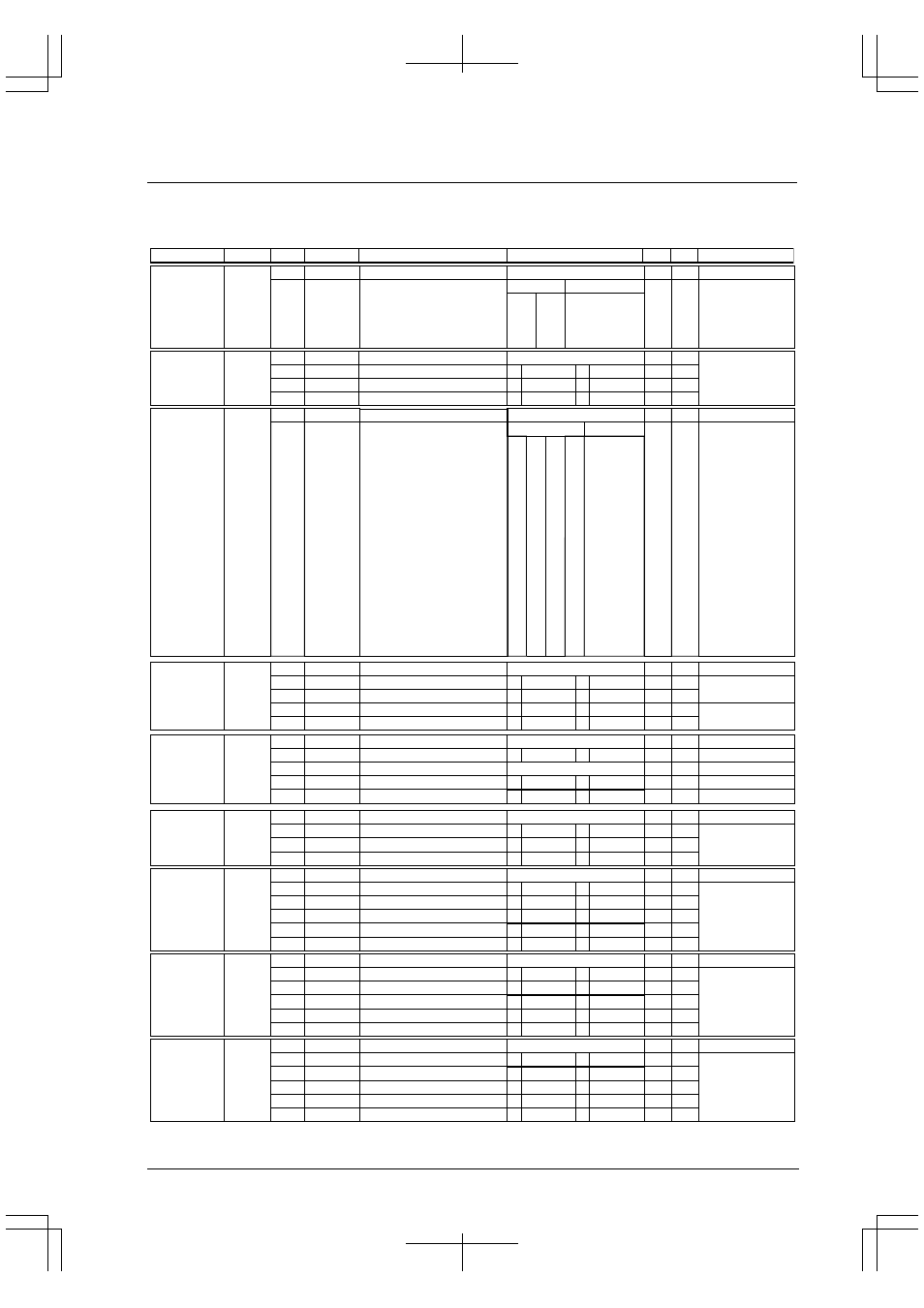

I/O Memory for Mobile Access Interfaces

Table 10.11 lists the contents of the I/O memory for mobile access interfaces.

Table 10.11 I/O Memory for Mobile Access Interfaces

Name

Address

Register name

Bit

Function

Setting

Init.

R/W

Remarks

–

MCRS1

MCRS0

D15–2

D1

D0

–

Communications macro select

1

1

0

0

1

0

1

0

MCRS[1:0]

–

Communications mode

PHS

PDC

HDLC

UART

–

0

0

–

R/W

0 when being read.

Only valid when

MSEL pin input is at

High level

0200000

(HW)

Communications

macro select

register

–

PHSRST

PDCRST

HDLRST

D15–3

D2

D1

D0

–

PHS block reset

PDC block reset

HDLC block reset

–

0

0

0

–

W

W

W

0 when being read.

0200002

(HW)

Software reset

register

–

1 Reset

0 Invalid

1 Reset

0 Invalid

1 Reset

0 Invalid

–

CKD3

CKD2

CKD1

CKD0

D15-4

D3

D2

D1

D0

–

Clock frequency divider

–

–

1

1

1

1

–

R/W

R/W

R/W

R/W

0 when being read.

fout = PERICLK

output

frequency

0200004

(HW)

Communications

block clock

frequency

divider register

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

CKD[3:0]

Frequency

fout/16

fout/15

fout/14

fout/13

fout/12

fout/11

fout/10

fout/9

fout/8

fout/7

fout/6

fout/5

fout/4

fout/3

fout/2

fout/2

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

–

MOPORT3

MOPORT2

CNT2

CNT1

D15–4

D3

D2

D1

D0

–

RTS output level

DTR output level

CNT2 output level

CNT1 output level

–

–

1

1

1

1

–

R/W

R/W

R/W

R/W

0 when being read.

Only valid for PHS, PDC,

and HDLC operation

Always valid

020000A

(HW)

Communications

block output port

data register

1 DTR="L"

0 DTR="H"

1 RTS="L"

0 RTS="H"

1 CNT2="L"

0 CNT2="H"

1 CNT1="L"

0 CNT1="H"

–

GOUTE

–

MIPORT1

MIPORT0

D15–8

D7

D6–2

D1

D0

–

GOUT output enable

–

DSR input level

RI input level

–

–

–

0

–

X

X

–

R/W

–

R

R

0 when being read.

0 when being read.

020000C

(HW)

Communications

block input port

data register

1 Enable

0 Disable

1 DSR="H"

0 DSR="L"

1 RI="H"

0 RI="L"

–

BMODE

BHALF

FMODE

D15–3

D2

D1

D0

–

Data conversion switch

Speed switch for data conversion

Frame frequency division switch

–

–

0

0

0

–

R/W

R/W

R/W

0 when being read.

0200010

(HW)

1 Convert

0 Pass through

1 32kbps

0 64kbps

1 Frequency divider 0 Pass through

Communications

block PHS mode

settings register

–

CP0EN4

CP0EN3

CP0EN2

CP0EN1

CP0EN0

D15–5

D4

D3

D2

D1

D0

–

Assign UINT4 to CP0

Assign UINT3 to CP0

Assign UINT2 to CP0

Assign UINT1 to CP0

Assign UINT0 to CP0

–

–

0

0

0

0

0

–

R/W

R/W

R/W

R/W

R/W

0 when being read.

CP0= CP0EN4

*

UINT4

+CP0EN3

*

UINT3

+CP0EN2

*

UINT2

+CP0EN1

*

UINT1

+CP0EN0

*

UINT0

0200020

(HW)

1 Enable

0 Disable

1 Enable

0 Disable

1 Enable

0 Disable

1 Enable

0 Disable

1 Enable

0 Disable

Communications

block CP0

interrupt select

register

–

CP1EN4

CP1EN3

CP1EN2

CP1EN1

CP1EN0

D15–5

D4

D3

D2

D1

D0

–

Assign UINT4 to CP1

Assign UINT3 to CP1

Assign UINT2 to CP1

Assign UINT1 to CP1

Assign UINT0 to CP1

–

–

0

0

0

0

0

–

R/W

R/W

R/W

R/W

R/W

0 when being read.

CP1= CP1EN4

*

UINT4

+CP1EN3

*

UINT3

+CP1EN2

*

UINT2

+CP1EN1

*

UINT1

+CP1EN0

*

UINT0

0200022

(HW)

1 Enable

0 Disable

1 Enable

0 Disable

1 Enable

0 Disable

1 Enable

0 Disable

1 Enable

0 Disable

Communications

block CP1

interrupt select

register

–

CP2EN4

CP2EN3

CP2EN2

CP2EN1

CP2EN0

D15–5

D4

D3

D2

D1

D0

–

Assign UINT4 to CP2

Assign UINT3 to CP2

Assign UINT2 to CP2

Assign UINT1 to CP2

Assign UINT0 to CP2

–

–

0

0

0

0

0

–

R/W

R/W

R/W

R/W

R/W

0 when being read.

CP2= CP2EN4

*

UINT4

+CP2EN3

*

UINT3

+CP2EN2

*

UINT2

+CP2EN1

*

UINT1

+CP2EN0

*

UINT0

0200024

(HW)

1 Enable

0 Disable

1 Enable

0 Disable

1 Enable

0 Disable

1 Enable

0 Disable

1 Enable

0 Disable

Communications

block CP2

interrupt select

register