I/o pins of hsdma, Dmareqx (dma request input pin), Dmaendx (end-of-transfer signal output pin) – Epson S1C33210 User Manual

Page 454: Method for setting hsdma i/o pins

V DMA BLOCK: HSDMA (High-Speed DMA)

B-V-2-2

EPSON

S1C33210 FUNCTION PART

I/O Pins of HSDMA

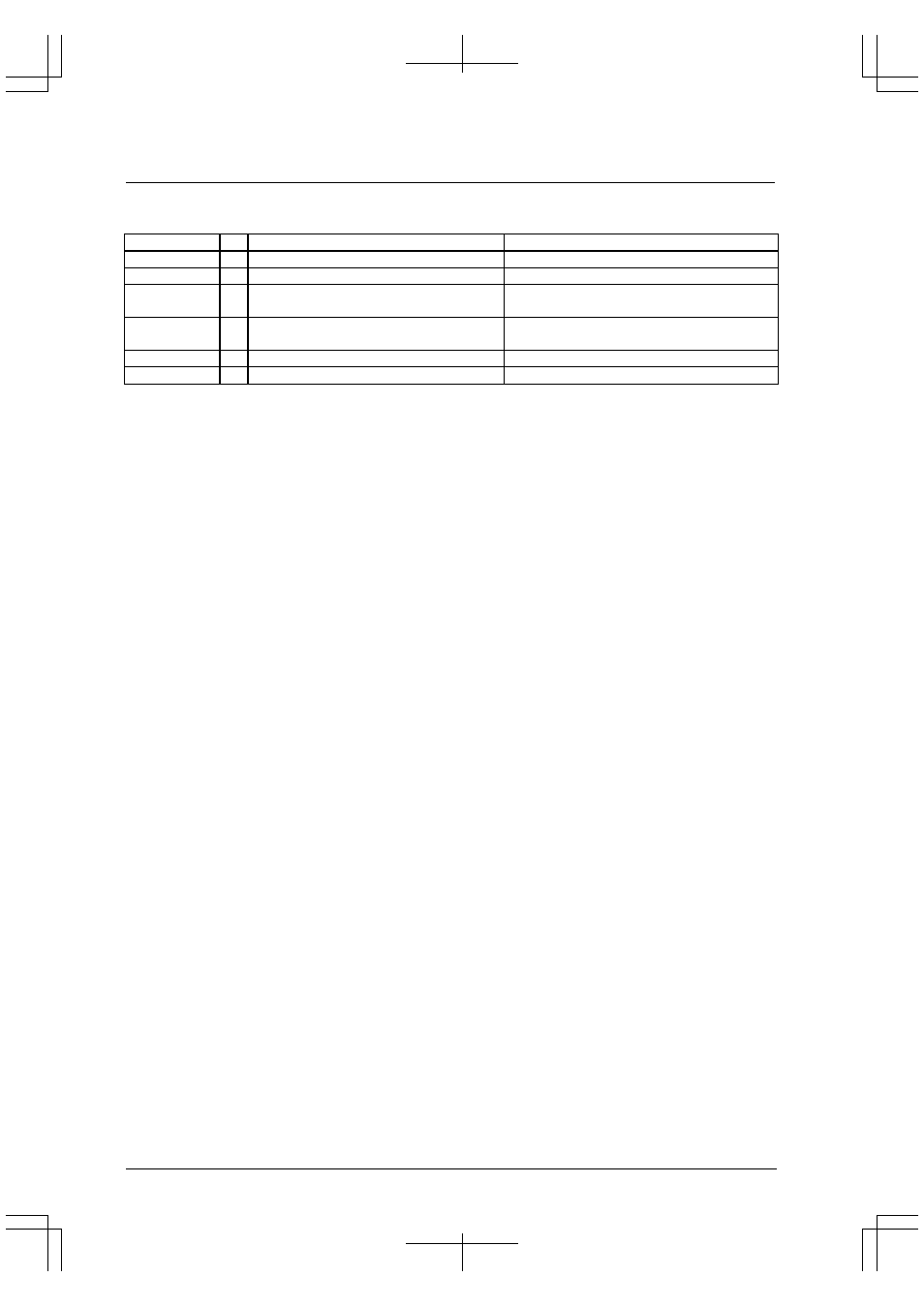

Table 2.1 lists the I/O pins used for HSDMA.

Table 2.1 I/O Pins of HSDMA

Pin name

I/O

Function

Function select bit

K50/#DMAREQ0

I

Input port / High-speed DMA request 0

CFK50(D0)/K5 function select register(0x402C0)

K51/#DMAREQ1

I

Input port / High-speed DMA request 1

CFK51(D1)/K5 function select register(0x402C0)

P15/EXCL4/

#DMAEND0

I/O I/O port / 16-bit timer 4 event counter input (I) /

#DMAEND0 output (O)

CFP15(D5)/P1 function select register(0x402D4)

P16/EXCL5/

#DMAEND1

I/O I/O port / 16-bit timer 5 event counter input (I) /

#DMAEND1 output (O)

CFP16(D6)/P1 function select register(0x402D4)

P32/#DMAACK0

I/O I/O port / #DMAACK0 output

CFP32(D2)/P3 function select register(0x402DC)

P33/#DMAACK1

I/O I/O port / #DMAACK1 output

CFP33(D3)/P3 function select register(0x402DC)

(I): Input mode, (O): Output mode, (Ex): Extended function

#DMAREQx (DMA request input pin)

This pin is used to input a DMA request signal from an external peripheral circuit. One data transfer operation

is performed by this trigger (either the rising edge or the falling edge of the signal can be selected). The

#DMAREQ0 to #DMAREQ1 pins correspond to channel 0 to channel 1, respectively.

In addition to this external input, software trigger or an interrupt factor can be selected for the HSDMA trigger

factor using the register in the interrupt controller.

#DMAACKx (DMA acknowledge signal output pin for single-address mode)

This signal is output to indicate that a DMA request has been acknowledged by the DMA controller.

In single-address mode, the I/O device that is the source or destination of transfer outputs data to the external bus

or takes in data from the external data synchronously with this signal.

The #DMAACK0 to #DMAACK1 pins correspond to channel 0 to channel 1, respectively.

This signal is not output in dual-address mode.

#DMAENDx (End-of-transfer signal output pin)

This signal is output to indicate that the number of data transfer operations that is set in the control register have

been completed. The #DMAEND0 to #DMAEND1 pins correspond to channel 0 to channel 1, respectively.

Method for setting HSDMA I/O pins

As shown in Table 2.1, the pins used for HSDMA are shared with input ports and I/O ports. At cold start, all of

these are set as input and I/O port pins (function select register = "0"). According to the signals to be used, set

the corresponding pin function select bit by writing "1". At hot start, the register retains the previous status

before a reset.

In addition, setup of the #DMAEND0 pin or #DMAEND1 pin further requires setting the I/O port's I/O control

bit IOC15 (D5) or IOC16 (D6) / P1 I/O control register (0x402D6) by writing "1" in order to direct the pin for

output. If this pin is directed for input, it functions as a 16-bit programmable timer's event counter input and

cannot be used to output the #DMAENDx signal. At cold start, this pin is set for input. At hot start, it retains

the previous status.