I-3 list of pins, List of external i/o pins – Epson S1C33210 User Manual

Page 133

I OUTLINE: LIST OF PINS

S1C33210 FUNCTION PART

EPSON

B-I-3-1

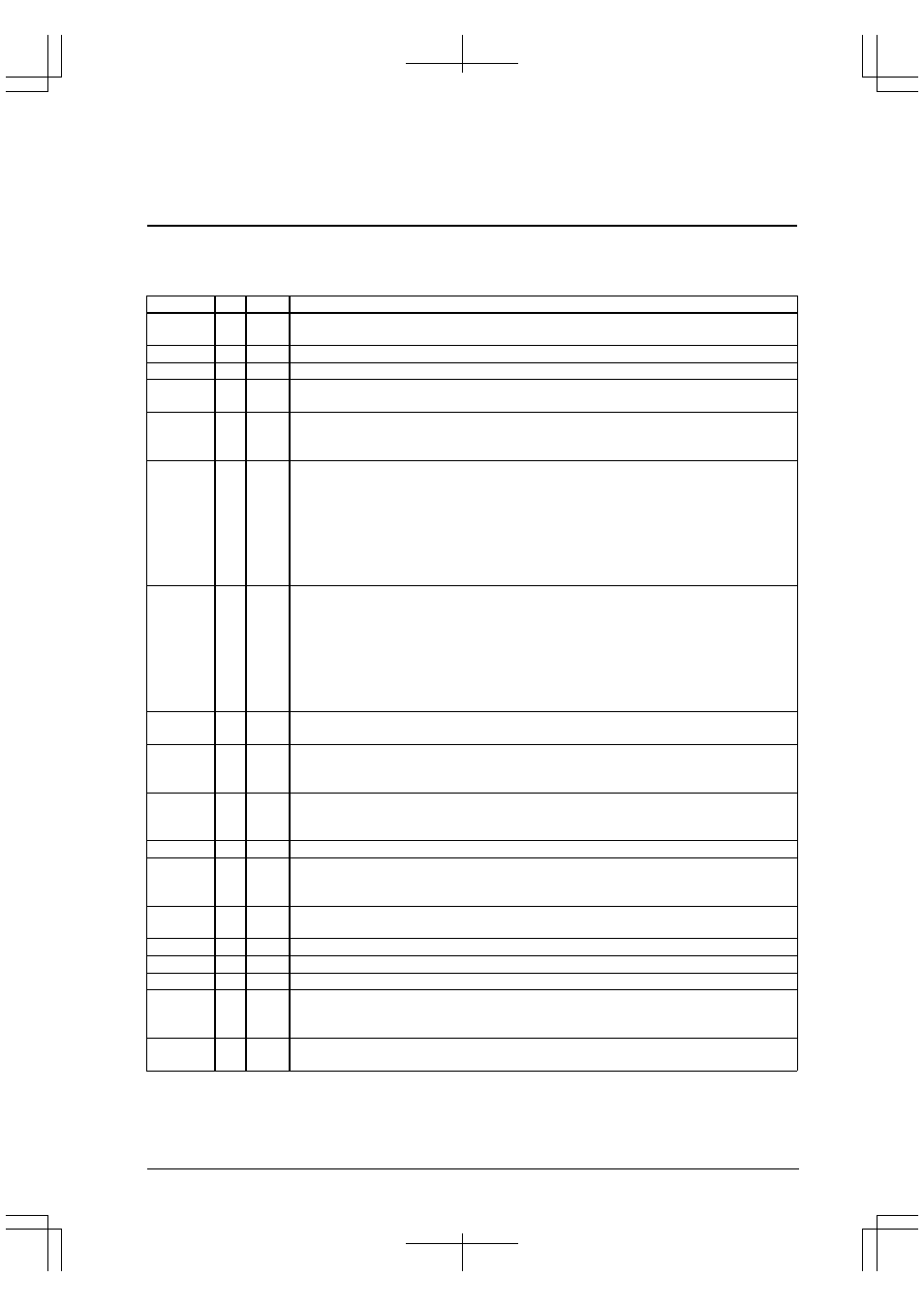

I-3 LIST OF PINS

List of External I/O Pins

The following lists the external I/O pins of the C33 Core Block and Peripheral Block. Note that some pins are listed

in two or more tables.

Table 3.1 List of Pins for External Bus Interface Signals

Pin name

I/O

Pull-up

Function

A0

#BSL

O

–

A0:

Address bus (A0) when SBUSST(D3/0x4812E) = "0" (default)

#BSL:

Bus strobe (low byte) signal when SBUSST(D3/0x4812E) = "1"

A[23:1]

O

–

Address bus (A1 to A23)

D[15:0]

I/O

–

Data bus (D0 to D15)

#CE10EX

O

–

Area 10 chip enable for external memory

*

When CEFUNC[1:0] = "1x", this pin outputs #CE9+#CE10EX signal.

#CE9

#CE17

O

–

#CE9:

Area 9 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "00" (default)

#CE17:

Area 17 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "01"

*

When CEFUNC[1:0] = "1x", this pin outputs #CE17+#CE18 signal.

#CE8

#RAS1

#CE14

#RAS3

O

–

#CE8:

Area 8 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "00" and A8DRA(D8/0x48128) = "0"

(default)

#RAS1:

Area 8 DRAM row strobe when CEFUNC[1:0](D[A:9])/0x48130) = "00" and

A8DRA(D8/0x48128) = "1"

#CE14:

Area 14 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "01" or "1x" and

A14DRA(D8/0x48122) = "0"

#RAS3:

Area 14 DRAM row strobe when CEFUNC[1:0](D[A:9])/0x48130) = "01"or "1x" and

A14DRA(D8/0x48122) = "1"

#CE7

#RAS0

#CE13

#RAS2

O

–

#CE7:

Area 7 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "00" and A7DRA(D7/0x48128) = "0"

(default)

#RAS0:

Area 7 DRAM row strobe when CEFUNC[1:0](D[A:9])/0x48130) = "00" and

A7DRA(D7/0x48128) = "1"

#CE13:

Area 13 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "01" or "1x" and

A13DRA(D7/0x48122) = "0"

#RAS2:

Area 13 DRAM row strobe when CEFUNC[1:0](D[A:9])/0x48130) = "01" or "1x" and

A13DRA(D7/0x48122) = "1"

#CE6

O

–

Area 6 chip enable

*

When CEFUNC[1:0] = "1x", this pin outputs #CE7+#CE8 signal.

#CE5

#CE15

O

–

#CE5:

Area 5 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "00" (default)

#CE15:

Area 15 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "01"

*

When CEFUNC[1:0] = "1x", this pin outputs #CE15+#CE16 signal.

#CE4

#CE11

O

–

#CE4:

Area 4 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "00" (default)

#CE11:

Area 11 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "01"

*

When CEFUNC[1:0] = "1x", this pin outputs #CE11+#CE12 signal.

#RD

O

–

Read signal

#WRL

#WR

#WE

O

–

#WRL:

Write (low byte) signal when SBUSST(D3/0x4812E) = "0" (default)

#WR:

Write signal when SBUSST(D3/0x4812E) = "1"

#WE:

DRAM write signal

#WRH

#BSH

O

–

#WRH:

Write (high byte) signal when SBUSST(D3/0x4812E) = "0" (default)

#BSH:

Bus strobe (high byte) signal when SBUSST(D3/0x4812E) = "1"

#HCAS

O

–

#HCAS:

DRAM column address strobe (high byte) signal

#LCAS

O

–

#LCAS:

DRAM column address strobe (low byte) signal

BCLK

O

–

Bus clock output

P34

#BUSREQ

#CE6

I/O

–

P34:

I/O port when CFP34(D4/0x402DC) = "0" (default)

#BUSREQ: Bus release request input when CFP34(D4/0x402DC) = "1"

#CE6:

Area 6 chip enable when CFP34(D4/0x402DC) = "1" and IOC34(D4/0x402DE) = "1"

P35

#BUSACK

I/O

–

P35:

I/O port when CFP35(D5/0x402DC) = "0" (default)

#BUSACK: Bus acknowledge output when CFP35(D5/0x402DC) = "1"