User interface signals – Epson S1C33210 User Manual

Page 154

II CORE BLOCK: BCU (Bus Control Unit)

B-II-4-2

EPSON

S1C33210 FUNCTION PART

User interface signals

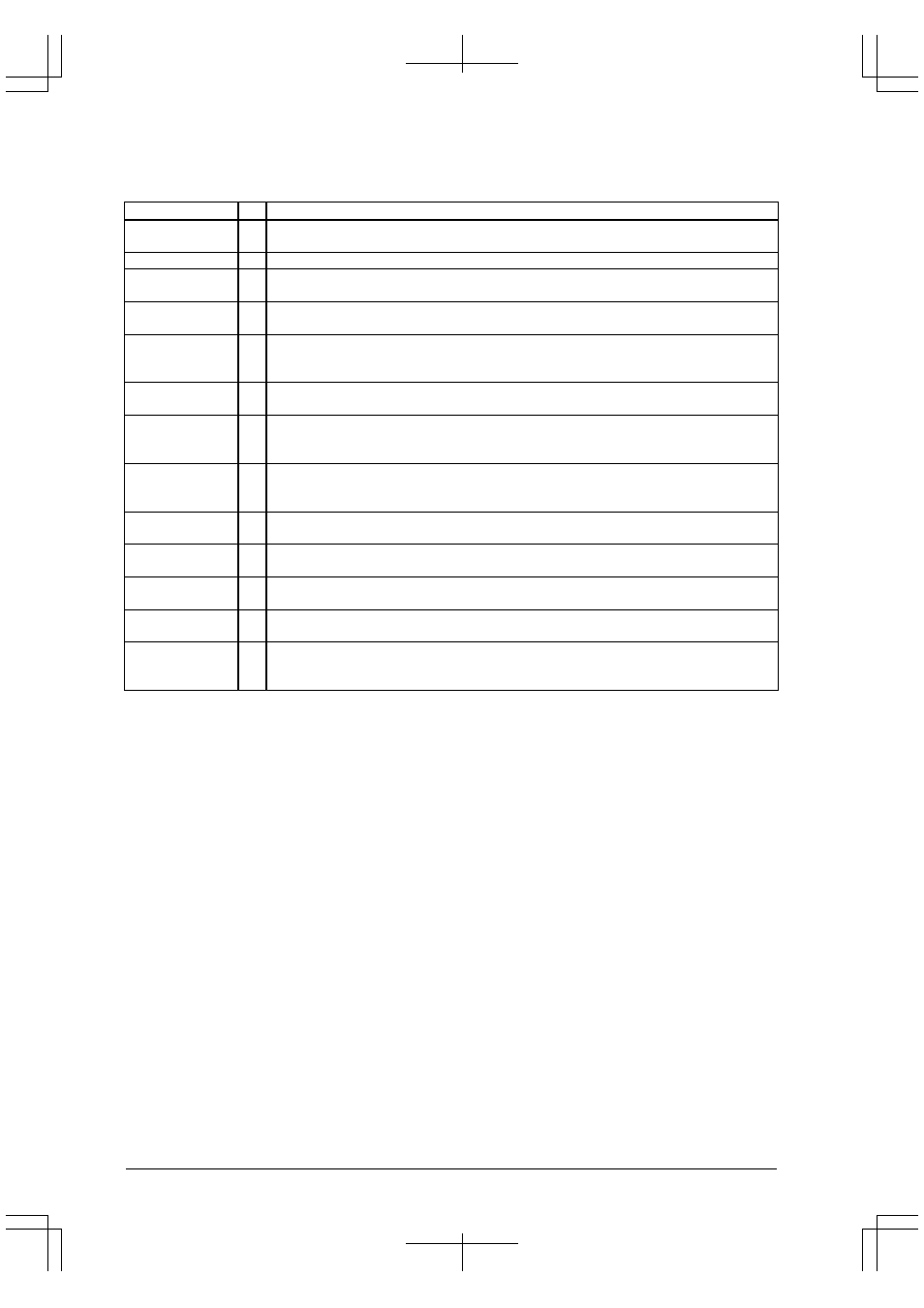

Table 4.2 List of User Interface Signals

Signal name

I/O

Function

Internal_addr0

O

• Address bus (a0) when SBUSST(D3/0x4812E) = "0" (default)

• Bus strobe (low byte) signal (#BSL) when SBUSST(D3/0x4812E) = "1"

Internal_addr[23:1]

O

Address bus (a1 to a23)

Internal_dout[15:0]

O

Output data bus (dout0 to dout15)

This data bus is used when the CPU writes data to the on-chip user logic.

Internal_din[15:0]

I

Input data bus (din0 to din15)

This data bus is used when the CPU reads data from the on-chip user logic.

Internal_ce4_x

Internal_ce5_x

Internal_ce6_x

O

Areas 6–4 chip enable signals

These signals go low when the CPU accesses the user logic circuits that are mapped to Areas 6–4.

Internal_rd_x

O

Read signal

This signal goes low when the CPU reads data from the user logic.

Internal_wrl_x

O

• Write (low byte) signal (#WRL) when SBUSST(D3/0x4812E) = "0" (default)

• Write signal (#WR) when SBUSST(D3/0x4812E) = "1"

This signal goes low when the CPU write 8 low-order bit data to the user logic.

Internal_wrh_x

O

• Write (high byte) signal (#WRH) when SBUSST(D3/0x4812E) = "0" (default)

• Bus strobe (high byte) signal (#BSH) when SBUSST(D3/0x4812E) = "1"

This signal goes low when the CPU write 8 high-order bit data to the user logic.

Internal_osc3_clk

O

High-speed (OSC3) oscillation clock output

This can be used as a source clock for the user logic.

Internal_pll_clk

O

PLL output clock

This can be used as a source clock for the user logic.

Internal_wait_x

I

Wait cycle request input

The user logic can request to insert wait cycles by setting this signal to low.

Internal_irrd_x

O

Instruction fetch indicator signal

This signal goes low when the CPU is in an instruction fetch cycle.

Internal_k60-k63

I

Input signals

These signals are connected to the input ports K60–K63. The user logic can request HSDMA, IDMA and

interrupts using these signals. The user logic can also be used as input ports with these signals.

The internal bus signals are available when an internal access area is set using the BCU register.

The bus conditions can be programmed using the BCU registers similar to the external bus.