I/o memory of intelligent dma, Trap vector, Table 3.3 shows the control bits of idma – Epson S1C33210 User Manual

Page 502

V DMA BLOCK: IDMA (Intelligent DMA)

B-V-3-14

EPSON

S1C33210 FUNCTION PART

Trap vector

The trap vector address for an interrupt upon completion of IDMA transfer by default is set to 0x0C00068.

The trap table base address can be changed using the TTBR registers (0x48134 to 0x48137).

I/O Memory of Intelligent DMA

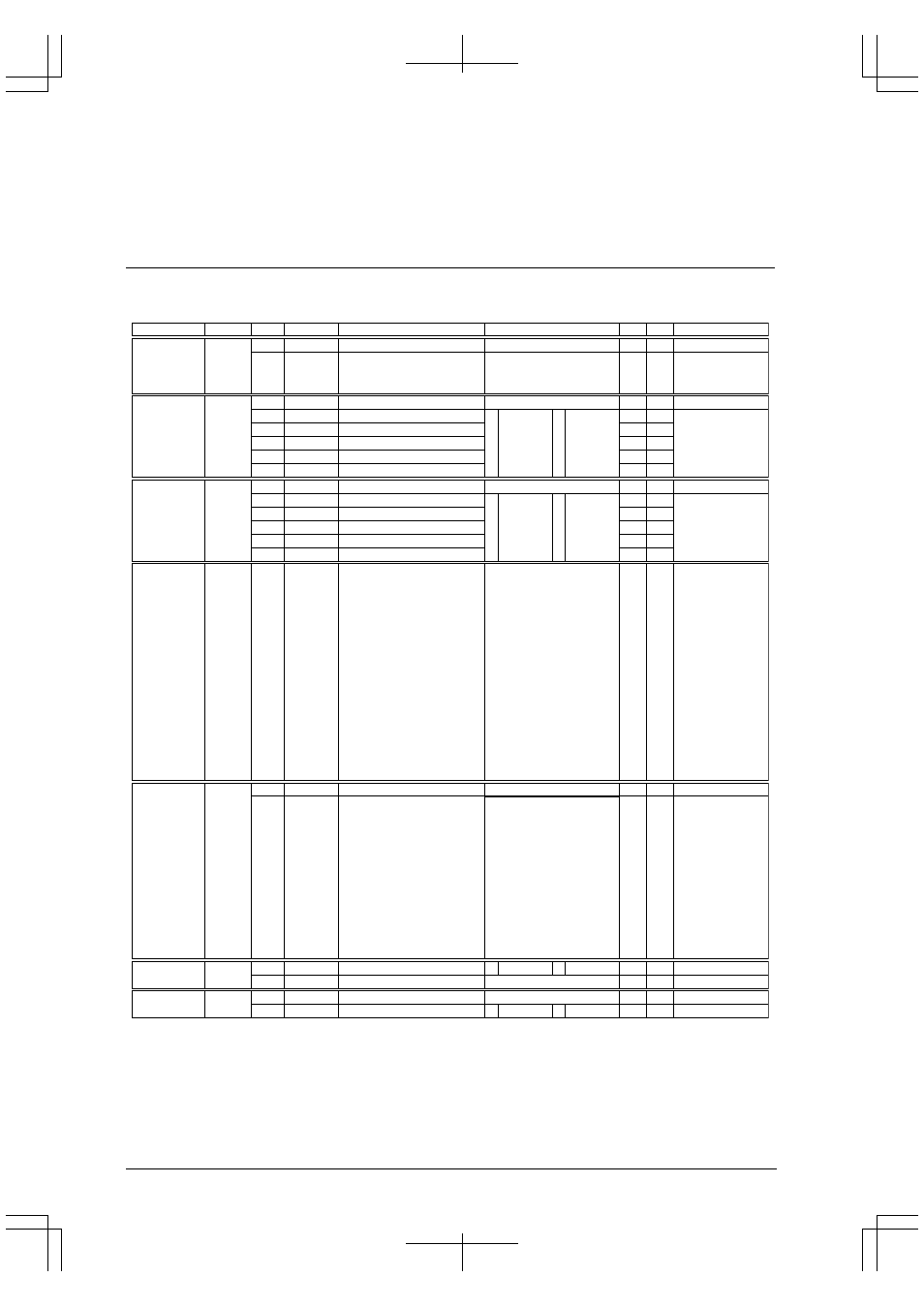

Table 3.3 shows the control bits of IDMA.

Table 3.3 Control Bits of IDMA

Name

Address

Register name

Bit

Function

Setting

Init.

R/W

Remarks

–

0 to 7

–

PDM2

PDM1

PDM0

D7–3

D2

D1

D0

reserved

IDMA interrupt level

–

X

X

X

–

R/W

0 when being read.

0040265

(B)

IDMA interrupt

priority register

–

EIDMA

EHDM3

EHDM2

EHDM1

EHDM0

D7–5

D4

D3

D2

D1

D0

reserved

IDMA

High-speed DMA Ch.3

High-speed DMA Ch.2

High-speed DMA Ch.1

High-speed DMA Ch.0

–

–

0

0

0

0

0

–

R/W

R/W

R/W

R/W

R/W

0 when being read.

0040271

(B)

1 Enabled

0 Disabled

DMA interrupt

enable register

–

FIDMA

FHDM3

FHDM2

FHDM1

FHDM0

D7–5

D4

D3

D2

D1

D0

reserved

IDMA

High-speed DMA Ch.3

High-speed DMA Ch.2

High-speed DMA Ch.1

High-speed DMA Ch.0

–

–

X

X

X

X

X

–

R/W

R/W

R/W

R/W

R/W

0 when being read.

0040281

(B)

DMA interrupt

factor flag

register

1 Factor is

generated

0 No factor is

generated

DBASEL15

DBASEL14

DBASEL13

DBASEL12

DBASEL11

DBASEL10

DBASEL9

DBASEL8

DBASEL7

DBASEL6

DBASEL5

DBASEL4

DBASEL3

DBASEL2

DBASEL1

DBASEL0

DF

DE

DD

DC

DB

DA

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

IDMA base address

low-order 16 bits

(Initial value: 0x0C003A0)

0

0

0

0

0

0

1

1

1

0

1

0

0

0

0

0

R/W

0048200

(HW)

IDMA base

address low-

order register

–

–

DBASEH11

DBASEH10

DBASEH9

DBASEH8

DBASEH7

DBASEH6

DBASEH5

DBASEH4

DBASEH3

DBASEH2

DBASEH1

DBASEH0

DF–C

DB

DA

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

reserved

IDMA base address

high-order 12 bits

(Initial value: 0x0C003A0)

–

0

0

0

0

1

1

0

0

0

0

0

0

–

R/W

Undefined in read.

0048202

(HW)

IDMA base

address

high-order

register

0 to 127

DSTART

DCHN

D7

D6–0

IDMA start

IDMA channel number

1 IDMA start

0 Stop

0

0

R/W

R/W

0048204

(B)

IDMA start

register

–

–

IDMAEN

D7–1

D0

reserved

IDMA enable

1 Enabled

0 Disabled

–

0

–

R/W

0048205

(B)

IDMA enable

register