Epson S1C33210 User Manual

Page 30

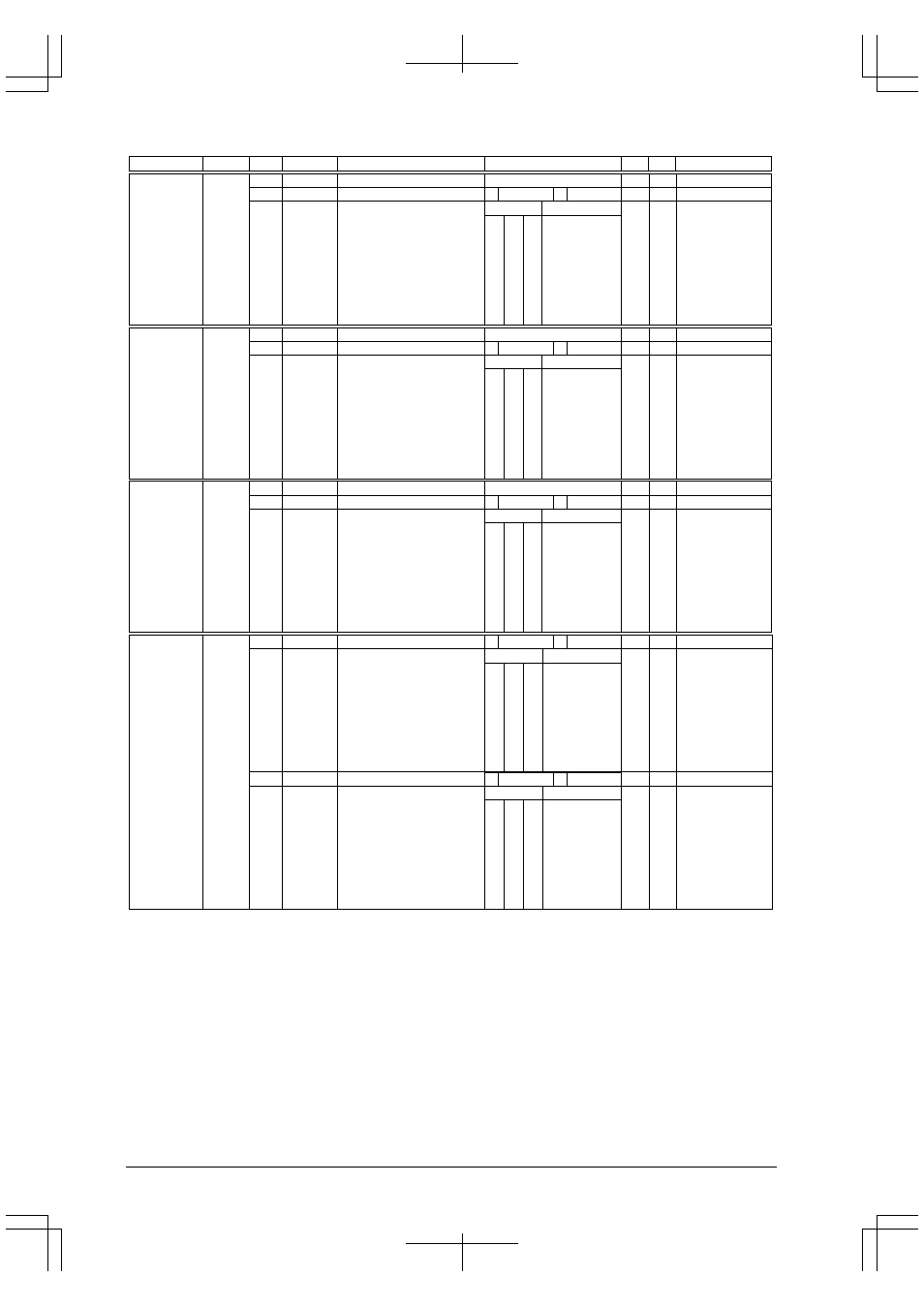

4 PERIPHERAL CIRCUITS

A-16

EPSON

S1C33210 PRODUCT PART

Name

Address

Register name

Bit

Function

Setting

Init.

R/W

Remarks

–

–

P16TON3

P16TS32

P16TS31

P16TS30

D7–4

D3

D2

D1

D0

reserved

16-bit timer 3 clock control

16-bit timer 3

clock division ratio selection

–

0

0

0

0

–

R/W

R/W

0 when being read.

θ

: selected by

Prescaler clock select

register (0x40181)

004014A

(B)

1 On

0 Off

1

1

1

1

0

0

0

0

1

1

0

0

1

1

0

0

1

0

1

0

1

0

1

0

P16TS3[2:0]

Division ratio

θ

/4096

θ

/1024

θ

/256

θ

/64

θ

/16

θ

/4

θ

/2

θ

/1

16-bit timer 3

clock control

register

–

–

P16TON4

P16TS42

P16TS41

P16TS40

D7–4

D3

D2

D1

D0

reserved

16-bit timer 4 clock control

16-bit timer 4

clock division ratio selection

–

0

0

0

0

–

R/W

R/W

0 when being read.

θ

: selected by

Prescaler clock select

register (0x40181)

004014B

(B)

1 On

0 Off

1

1

1

1

0

0

0

0

1

1

0

0

1

1

0

0

1

0

1

0

1

0

1

0

P16TS4[2:0]

Division ratio

θ

/4096

θ

/1024

θ

/256

θ

/64

θ

/16

θ

/4

θ

/2

θ

/1

16-bit timer 4

clock control

register

–

–

P16TON5

P16TS52

P16TS51

P16TS50

D7–4

D3

D2

D1

D0

reserved

16-bit timer 5 clock control

16-bit timer 5

clock division ratio selection

–

0

0

0

0

–

R/W

R/W

0 when being read.

θ

: selected by

Prescaler clock select

register (0x40181)

004014C

(B)

1 On

0 Off

1

1

1

1

0

0

0

0

1

1

0

0

1

1

0

0

1

0

1

0

1

0

1

0

P16TS5[2:0]

Division ratio

θ

/4096

θ

/1024

θ

/256

θ

/64

θ

/16

θ

/4

θ

/2

θ

/1

16-bit timer 5

clock control

register

1 On

0 Off

P8TON1

P8TS12

P8TS11

P8TS10

P8TON0

P8TS02

P8TS01

P8TS00

D7

D6

D5

D4

D3

D2

D1

D0

8-bit timer 1 clock control

8-bit timer 1

clock division ratio selection

8-bit timer 0 clock control

8-bit timer 0

clock division ratio selection

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

θ

: selected by

Prescaler clock select

register (0x40181)

8-bit timer 1 can

generate the OSC3

oscillation-stabilize

waiting period.

θ

: selected by

Prescaler clock select

register (0x40181)

8-bit timer 0 can

generate the DRAM

refresh clock.

004014D

(B)

1

1

1

1

0

0

0

0

1

1

0

0

1

1

0

0

1

0

1

0

1

0

1

0

P8TS1[2:0]

Division ratio

θ

/4096

θ

/2048

θ

/1024

θ

/512

θ

/256

θ

/128

θ

/64

θ

/32

1 On

0 Off

1

1

1

1

0

0

0

0

1

1

0

0

1

1

0

0

1

0

1

0

1

0

1

0

P8TS0[2:0]

Division ratio

θ

/256

θ

/128

θ

/64

θ

/32

θ

/16

θ

/8

θ

/4

θ

/2

8-bit timer 0/1

clock control

register