Epson S1C33210 User Manual

Page 554

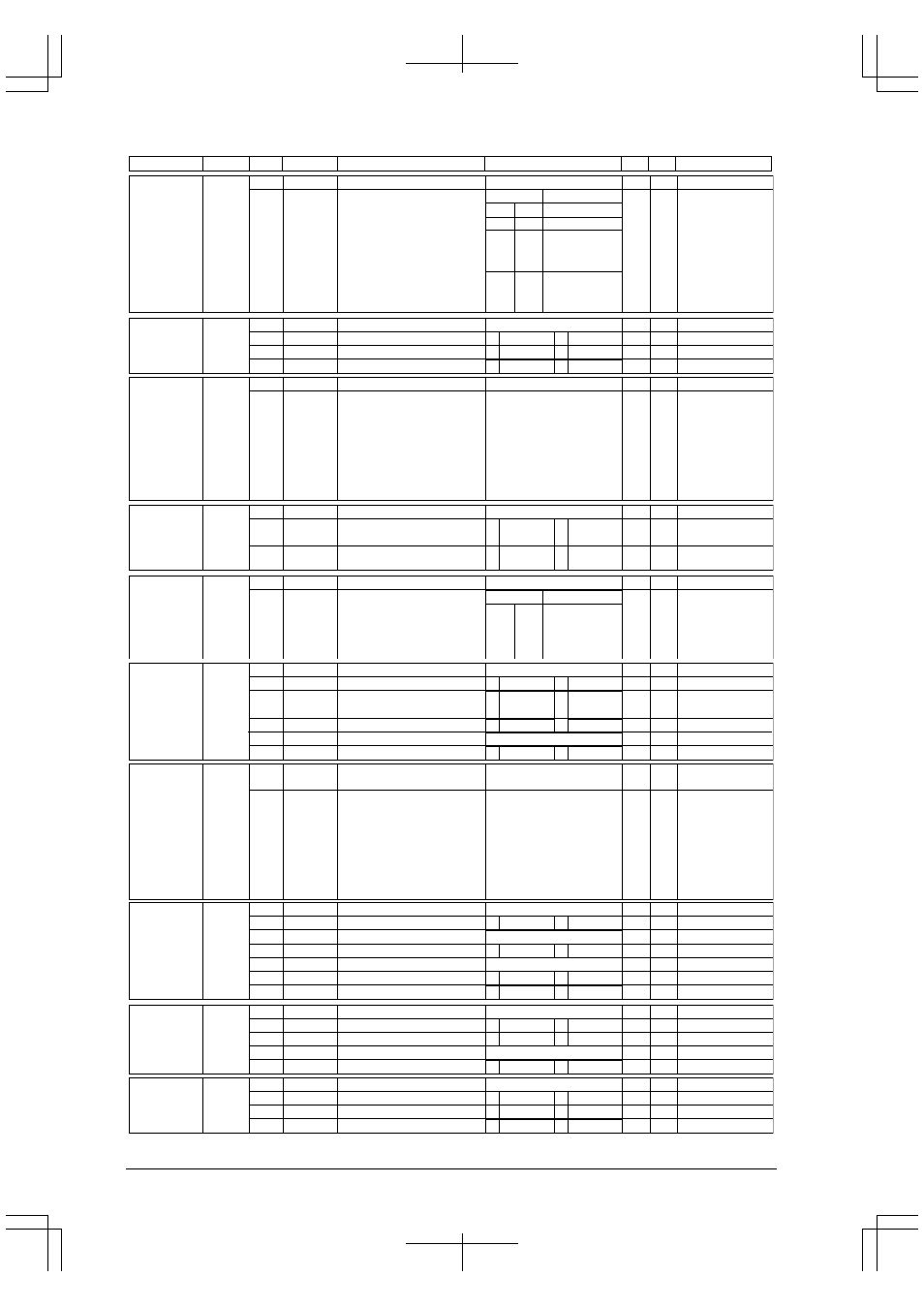

APPENDIX: I/O MAP

B-APPENDIX-46

EPSON

S1C33210 FUNCTION PART

Name

Address

Register name

Bit

Function

Setting

Init.

R/W

Remarks

–

RXINTS1

RXINTS0

D15–2

D1

D0

–

Receive interrupt operating mode

–

0

0

–

R/W

R/W

0 when being read.

0200312

(HW)

HDLC receive

interrupt mode

settings

register

–

1

1

0

0

1

0

1

0

RXINTS[1:0] Operating Mode

(Not allowed)

Sp INT Only

Rx INT and Sp

INT On FIFO

Threshold Level

Rx INT and Sp

INT On First Rx

Character

–

RXFR

ENTHM

RXINXT

D15–3

D2

D1

D0

–

Receive queue reset

Enter Hunt mode

Specify next receive interrupt

–

0

0

0

–

W

W

W

0 when being read.

0200314

(HW)

HDLC receive

control register

–

1 Reset

0 Ignored

1 Force shift

0 Ignored

1 Specify interrupt 0 Ignored

–

RXD7

RXD6

RXD5

RXD4

RXD3

RXD2

RXD1

RXD0

D15–8

D7

D6

D5

D4

D3

D2

D1

D0

–

HDLC receive data

RXD7 = MSB

RXD0 = LSB

–

X

X

X

X

X

X

X

X

–

R

0 when being read.

0200316

(HW)

–

0x00 to 0xFF

HDLC receive

data register

–

ABTCRC

MRKFLG

D15–2

D1

D0

–

Transmit pattern for TXUDR

Transmit pattern for idle state

–

0

0

–

R/W

R/W

0 when being read.

0200318

(HW)

1 Transmit abort

and flag patterns

0 Transmit CRC

and flag

1 Transmit

mark pattern

0 Transmit flag

–

HDLC transmit

operation

settings

register

–

TXFTH1

TXFTH0

D15–2

D1

D0

–

Transmit queue interrupt level

–

1

1

0

0

1

0

1

0

TXFTH[1:0]

Level

1 empty

2 empty

3 empty

All 4 empty

–

0

0

–

R/W

R/W

0 when being read.

020031A

(HW)

HDLC transmit

queue

threshold

register

–

RTXUEL

SNDABT

TXFR

–

RTXU

D15–8

D7

D6

D5

D4–1

D0

–

HDLC reset TXUDR/EOM latch

HDLC transmit abort setting

HDLC transmit queue reset

–

HDLC reset TXUDR flag

–

–

–

0

0

0

–

0

–

W

W

W

–

W

0 when being read.

Writes of "0" are ignored

Writes of "0" are ignored

Writes of "0" are ignored

0 when being read.

Writes of "0" are ignored

020031C

(HW)

1 Reset latch

0 Ignored

1 Transmit

abort pattern

0 Ignored

1 Reset queue

0 Ignored

1 Reset flag

0 Ignored

HDLC transmit

control register

–

TXD7

TXD6

TXD5

TXD4

TXD3

TXD2

TXD1

TXD0

D15–8

D7

D6

D5

D4

D3

D2

D1

D0

–

HDLC transmit data

TXD7 = MSB

TXD0 = LSB

–

X

X

X

X

X

X

X

X

–

W

Indeterminate value

when read

Indeterminate value

when read

020031E

(HW)

–

0x00 to 0xFF

HDLC transmit

data register

–

ABORT

–

TXUE

–

HUNT

IDLED

D15–8

D7

D6

D5

D4–2

D1

D0

–

Abort pattern detected

–

Tx underrun/EOM detected

–

Hunt state

Idle pattern detected

–

X

–

X

–

X

X

–

R

–

R

–

R

R

0 when being read.

0 when being read.

0 when being read.

020032C

(HW)

1 Detected

0 Not detected

1 Detected

0 Not detected

1 Hunting

0 Not hunting

1 Detected

0 Not detected

HDLC E/S INT

receive status

register

–

–

–

–

RXOVR

EOF

–

SHFD

D15–8

D7

D6

D5–1

D0

–

Receive data overrun detected

End of frame detected

–

Short frame detected

–

–

–

X

X

–

X

–

R

R

–

R

0 when being read.

0 when being read.

020032E

(HW)

HDLC Sp INT

receive status

register

1 Detected

0 Not detected

1 Detected

0 Not detected

1 Detected

0 Not detected

–

RESID

RCA

CRCER

D15–3

D2

D1

D0

–

Residue code detected

Receive character available

CRC error detected

–

X

X

X

–

R

R

R

0 when being read.

0200330

(HW)

HDLC receive

status register

–

1 Detected

0 Not detected

1 Available

0 Not available

1 Detected

0 Not detected