Ii-4 bcu (bus control unit), Pin assignment for external system interface, I/o pin list – Epson S1C33210 User Manual

Page 153: External i/o pins

II CORE BLOCK: BCU (Bus Control Unit)

S1C33210 FUNCTION PART

EPSON

B-II-4-1

II-4 BCU (Bus Control Unit)

The BCU (Bus Control Unit) provides an interface for external devices and on-chip user logic block. The types

and sizes of memory and peripheral I/O devices can be set for each area of the memory map and can be controlled

directly by the BCU. This unit also supports a direct interface for DRAM and burst ROM. This chapter describes how

to control the external and internal system interface, and how it operates.

Note: The control registers of the external system interface shown in this chapter are mapped to the

internal 16-bit I/O area. Therefore, the addresses of these control registers are indicated by half-

word (16-bit) addresses unless otherwise specified. Note that the control registers can be accessed

in bytes, half-words, or words.

Pin Assignment for External System Interface

I/O Pin List

External I/O pins

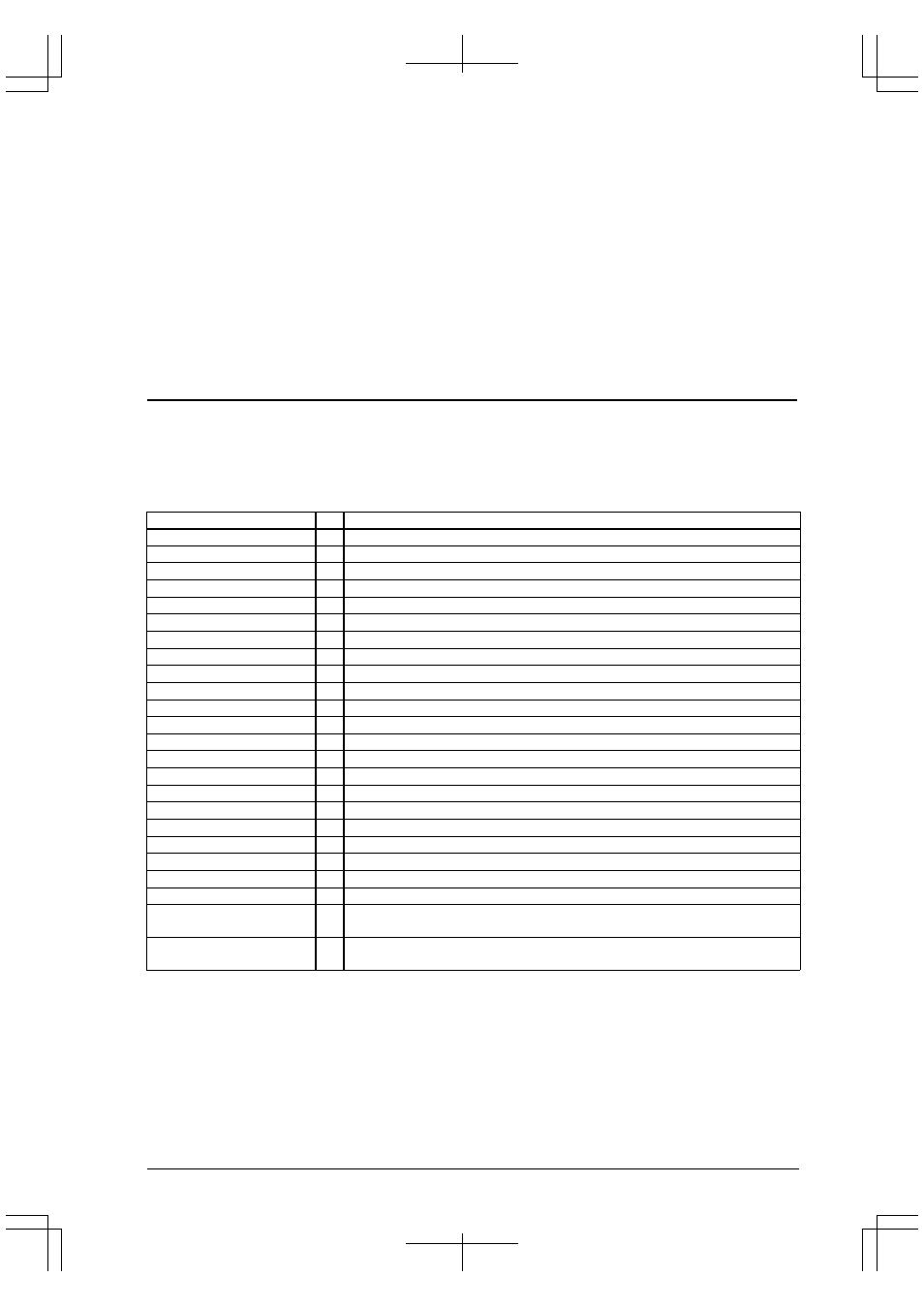

Table 4.1 lists the pins used for the external system interface.

Table 4.1 I/O Pin List

Pin name

I/O

Function

A[0]/#BSL

O

Address bus (A0) / Bus strobe (Low-byte)

A[23:1]

O

Address bus (A1–A23)

D[15:0]

I/O Data bus (D0–D15)

#CE10EX

O

Area 10 external memory chip enable

#CE9/#CE17

O

Area 9/17 chip enable

#CE8/#RAS1/#CE14/#RAS3

O

Area 8/14 chip enable / DRAM Row strobe

#CE7/#RAS0/#CE13/#RAS2

O

Area 7/13 chip enable / DRAM Row strobe

#CE6

O

Area 6 chip enable

#CE5/#CE15

O

Area 5/15 chip enable

#CE4/#CE11

O

Area 4/11 chip enable

#CE3

O

Area 3 chip enable for ROM emulation mode

#RD

O

Read signal

#WRL/#WR/#WE

O

Write (Low-byte) / Write / DRAM write

#WRH/#BSH

O

Write (High-byte) / Bus strobe (High-byte)

#HCAS

O

DRAM column address strobe (High-byte)

#LCAS

O

DRAM column address strobe (Low-byte)

BCLK

O

Bus clock output

#BUSREQ/#CE6/P34

I/O Bus release request / Area 6 chip enable / I/O port

#BUSACK/P35

O

Bus request acknowledge / I/O port

#WAIT/#CE4&5/P30

I/O Wait cycle request / Areas 4&5 chip enable / I/O port

#DRD/P20

O

DRAM read signal / I/O port

#DWE/P21

O

DRAM write (Low-byte) / I/O port

#X2SPD

I

CPU - BCLK clock ratio

1: CPU clock = Bus clock, 0: CPU clock = Bus clock

×

2

EA10MD[1:0]

I

Area 10 boot mode selection

11: External ROM, 10: Internal ROM, 01: OTP, 00: Internal ROM emulation