Epson S1C33210 User Manual

Page 380

III PERIPHERAL BLOCK: INPUT/OUTPUT PORTS

B-III-9-18

EPSON

S1C33210 FUNCTION PART

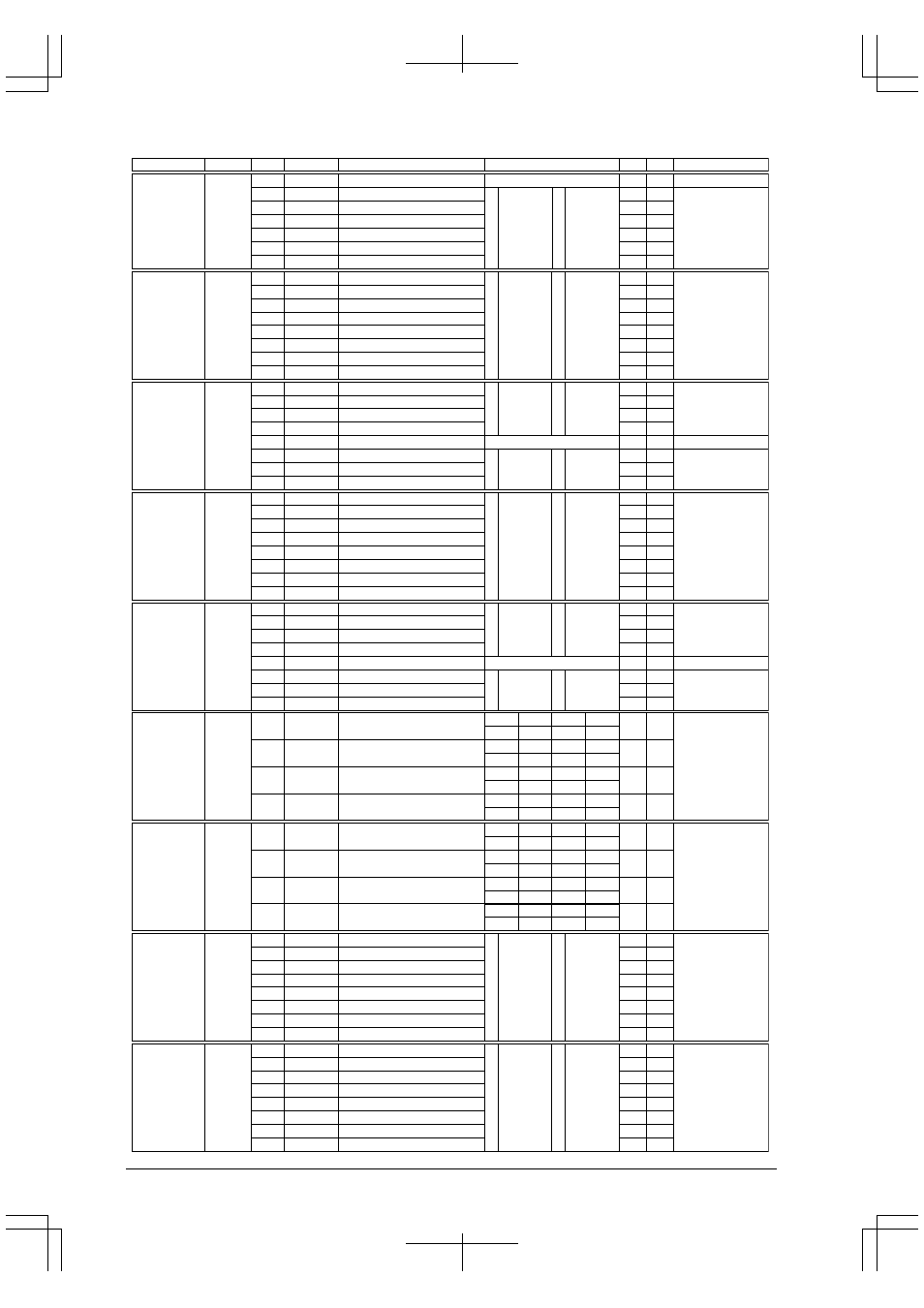

Name

Address

Register name

Bit

Function

Setting

Init.

R/W

Remarks

–

FP7

FP6

FP5

FP4

FCTM

FADE

D7–6

D5

D4

D3

D2

D1

D0

reserved

Port input 7

Port input 6

Port input 5

Port input 4

Clock timer

A/D converter

–

–

X

X

X

X

X

X

–

R/W

R/W

R/W

R/W

R/W

R/W

0 when being read.

0040287

(B)

1 Factor is

generated

0 No factor is

generated

Port input 4–7,

clock timer, A/D

interrupt factor

flag register

R16TC0

R16TU0

RHDM1

RHDM0

RP3

RP2

RP1

RP0

D7

D6

D5

D4

D3

D2

D1

D0

16-bit timer 0 comparison A

16-bit timer 0 comparison B

High-speed DMA Ch.1

High-speed DMA Ch.0

Port input 3

Port input 2

Port input 1

Port input 0

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

0040290

(B)

1 IDMA

request

0 Interrupt

request

Port input 0–3,

high-speed

DMA Ch. 0/1,

16-bit timer 0

IDMA request

register

RP7

RP6

RP5

RP4

–

RADE

RSTX1

RSRX1

D7

D6

D5

D4

D3

D2

D1

D0

Port input 7

Port input 6

Port input 5

Port input 4

reserved

A/D converter

SIF Ch.1 transmit buffer empty

SIF Ch.1 receive buffer full

0

0

0

0

–

0

0

0

R/W

R/W

R/W

R/W

–

R/W

R/W

R/W

0 when being read.

0040293

(B)

1 IDMA

request

0 Interrupt

request

1 IDMA

request

0 Interrupt

request

–

Serial I/F Ch.1,

A/D,

port input 4–7

IDMA request

register

DE16TC0

DE16TU0

DEHDM1

DEHDM0

DEP3

DEP2

DEP1

DEP0

D7

D6

D5

D4

D3

D2

D1

D0

16-bit timer 0 comparison A

16-bit timer 0 comparison B

High-speed DMA Ch.1

High-speed DMA Ch.0

Port input 3

Port input 2

Port input 1

Port input 0

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

0040294

(B)

1 IDMA

enabled

0 IDMA

disabled

Port input 0–3,

high-speed

DMA Ch. 0/1,

16-bit timer 0

IDMA enable

register

DEP7

DEP6

DEP5

DEP4

–

DEADE

DESTX1

DESRX1

D7

D6

D5

D4

D3

D2

D1

D0

Port input 7

Port input 6

Port input 5

Port input 4

reserved

A/D converter

SIF Ch.1 transmit buffer empty

SIF Ch.1 receive buffer full

0

0

0

0

–

0

0

0

R/W

R/W

R/W

R/W

–

R/W

R/W

R/W

0 when being read.

0040297

(B)

1 IDMA

enabled

0 IDMA

disabled

1 IDMA

enabled

0 IDMA

disabled

–

Serial I/F Ch.1,

A/D,

port input 4–7

IDMA enable

register

SPT31

SPT30

SPT21

SPT20

SPT11

SPT10

SPT01

SPT00

D7

D6

D5

D4

D3

D2

D1

D0

FPT3 interrupt input port selection

FPT2 interrupt input port selection

FPT1 interrupt input port selection

FPT0 interrupt input port selection

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

00402C6

(B)

Port input

interrupt select

register 1

11

10

01

00

P23

P03

CP4

K63

11

10

01

00

P22

P02

K52

K62

11

10

01

00

P21

P01

K51

K61

11

10

01

00

P20

P00

K50

K60

11

10

01

00

P27

–

P33

CP3

11

10

01

00

P26

–

P32

CP2

11

10

01

00

P25

P05

P31

CP1

11

10

01

00

P24

P04

–

CP0

SPT71

SPT70

SPT61

SPT60

SPT51

SPT50

SPT41

SPT40

D7

D6

D5

D4

D3

D2

D1

D0

FPT7 interrupt input port selection

FPT6 interrupt input port selection

FPT5 interrupt input port selection

FPT4 interrupt input port selection

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

00402C7

(B)

Port input

interrupt select

register 2

1

High level

or

Rising edge

0

Low level

or

Falling

edge

SPPT7

SPPT6

SPPT5

SPPT4

SPPT3

SPPT2

SPPT1

SPPT0

D7

D6

D5

D4

D3

D2

D1

D0

FPT7 input polarity selection

FPT6 input polarity selection

FPT5 input polarity selection

FPT4 input polarity selection

FPT3 input polarity selection

FPT2 input polarity selection

FPT1 input polarity selection

FPT0 input polarity selection

1

1

1

1

1

1

1

1

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

00402C8

(B)

Port input

interrupt

input polarity

select register

1 Edge

0 Level

SEPT7

SEPT6

SEPT5

SEPT4

SEPT3

SEPT2

SEPT1

SEPT0

D7

D6

D5

D4

D3

D2

D1

D0

FPT7 edge/level selection

FPT6 edge/level selection

FPT5 edge/level selection

FPT4 edge/level selection

FPT3 edge/level selection

FPT2 edge/level selection

FPT1 edge/level selection

FPT0 edge/level selection

1

1

1

1

1

1

1

1

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

00402C9

(B)

Port input

interrupt

edge/level

select register