Epson S1C33210 User Manual

Page 555

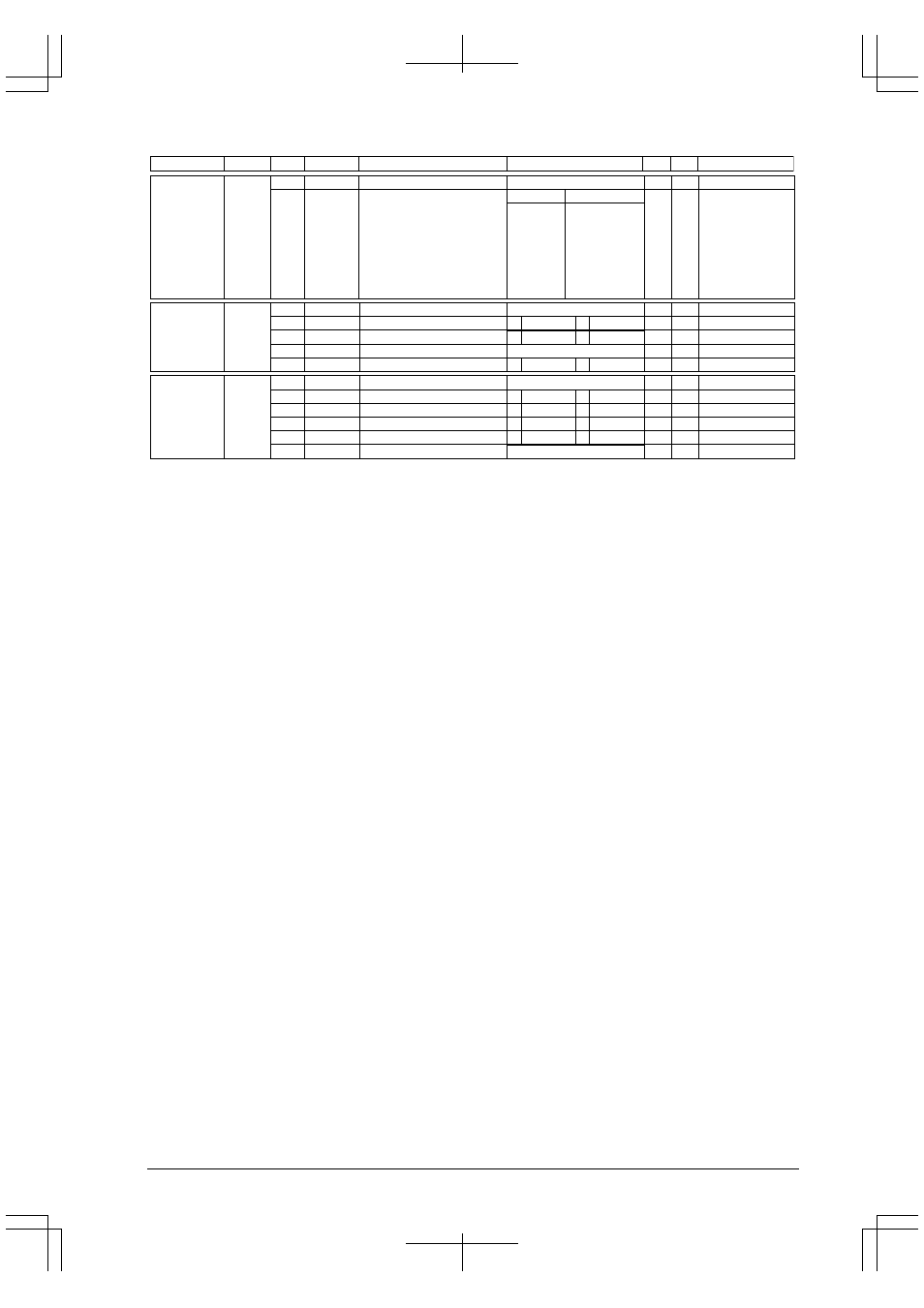

APPENDIX: I/O MAP

S1C33210 FUNCTION PART

EPSON

B-APPENDIX-47

Name

Address

Register name

Bit

Function

Setting

Init.

R/W

Remarks

–

RCODE7

RCODE6

RCODE5

RCODE4

RCODE3

RCODE2

RCODE1

RCODE0

D15–8

D7

D6

D5

D4

D3

D2

D1

D0

–

Residue Code

Number of valid bits in excess

residue code bits at end of frame

–

11111110

11111100

11111000

11110000

11100000

11000000

10000000

RCODE[7:0]

Effective bits

7

6

5

4

3

2

1

–

X

X

X

X

X

X

X

X

–

R

0 when being read.

Only valid when

RESID = 1

0200332

(HW)

HDLC residue

code register

–

TXUE

TXBRDY

–

TXUDR

D15–8

D7

D6

D5–1

D0

–

Tx underrun/EOM detected

Transmit queue not full

–

Transmit queue underrun

–

–

–

X

X

–

X

–

R

R

–

R

0 when being read.

0 when being read.

0200334

(HW)

HDLC transmit

status register

1 not Full

0 Full

1 Yes

0 No

1 Under run

0 No underrun

–

ESINT

SPINT

RXINT

TXINT

–

D15–8

D7

D6

D5

D4

D3–0

–

E/S INT interrupt

Sp INT interrupt

Rx INT interrupt

Tx INT interrupt

–

–

–

–

X

X

X

X

–

–

R

R

R

R

–

0 when being read.

0 when being read.

0200336

(HW)

1 Request pending 0 No interrupts

1 Request pending 0 No interrupts

1 Request pending 0 No interrupts

1 Request pending 0 No interrupts

HDLC monitor

register