A.5 sram (70ns), Sram interface setup examples – 70ns, Sram interface timing – 70ns – Epson S1C33210 User Manual

Page 118: Sram: 70ns, cpu: 33mhz, read cycle, Sram: 70ns, cpu: 33mhz, write cycle

APPENDIX A

A-104

EPSON

S1C33210 PRODUCT PART

A.5 SRAM (70ns)

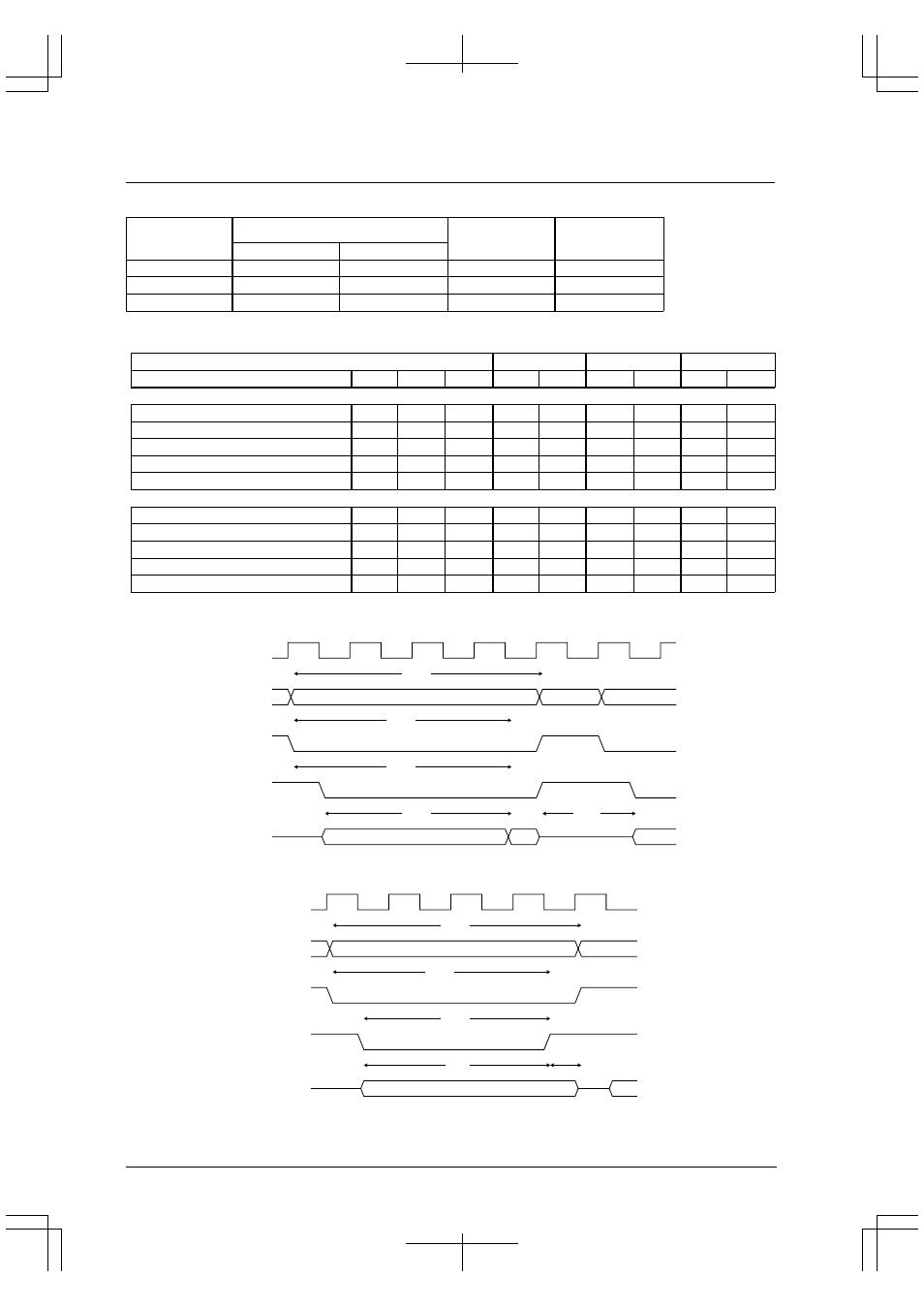

SRAM interface setup examples – 70ns

Operating

Read cycle

Write cycle

Output disable

frequency

Wait cycle

Read cycle

delay time

20MHz

2

3

3

1.5

25MHz

2

3

3

1.5

33MHz

3

4

4

1.5

SRAM interface timing – 70ns

SRAM interface

33MHz

25MHz

20MHz

Parameter

Symbol

Min.

Max.

Cycle

Time

Cycle

Time

Cycle

Time

Read cycle time

t

RC

70

–

4

120

3

120

3

150

Address access time

t

ACC

–

70

4

120

3

120

3

150

#CE access time

t

ACS

–

70

4

120

3

120

3

150

#OE access time

t

OE

–

40

3.5

105

2.5

100

2.5

125

Output disable delay time

t

OHZ

0

30

1.5

45

1.5

60

1.5

75

Write cycle time

t

WC

70

–

4

120

3

120

3

150

Address enable time

t

AW

60

–

3.5

105

2.5

100

2.5

125

Write pulse width

t

WP

55

–

3

90

2

80

2

100

Input data setup time

t

DW

30

–

3

90

2

80

2

100

Input data hold time

t

DH

0

–

0.5

15

0.5

20

0.5

25

SRAM: 70ns, CPU: 33MHz, read cycle

t

RC

t

ACC

t

ACS

t

OE

BCLK

A[23:0]

#CEx

#RD

D[15:0]

RD data

;;;;;

;;;;;

;;;;;;;;;;;;;

;;;;;;;;;;;;;

;;;;

;;;;

t

OHZ

SRAM: 70ns, CPU: 33MHz, write cycle

t

WC

t

AW

t

WP

t

DW

BCLK

A[23:0]

#CEx

#WP

D[15:0]

WR data

;;;;;

;;;;;

;;;

;;;

t

DH