Epson S1C33210 User Manual

Page 123

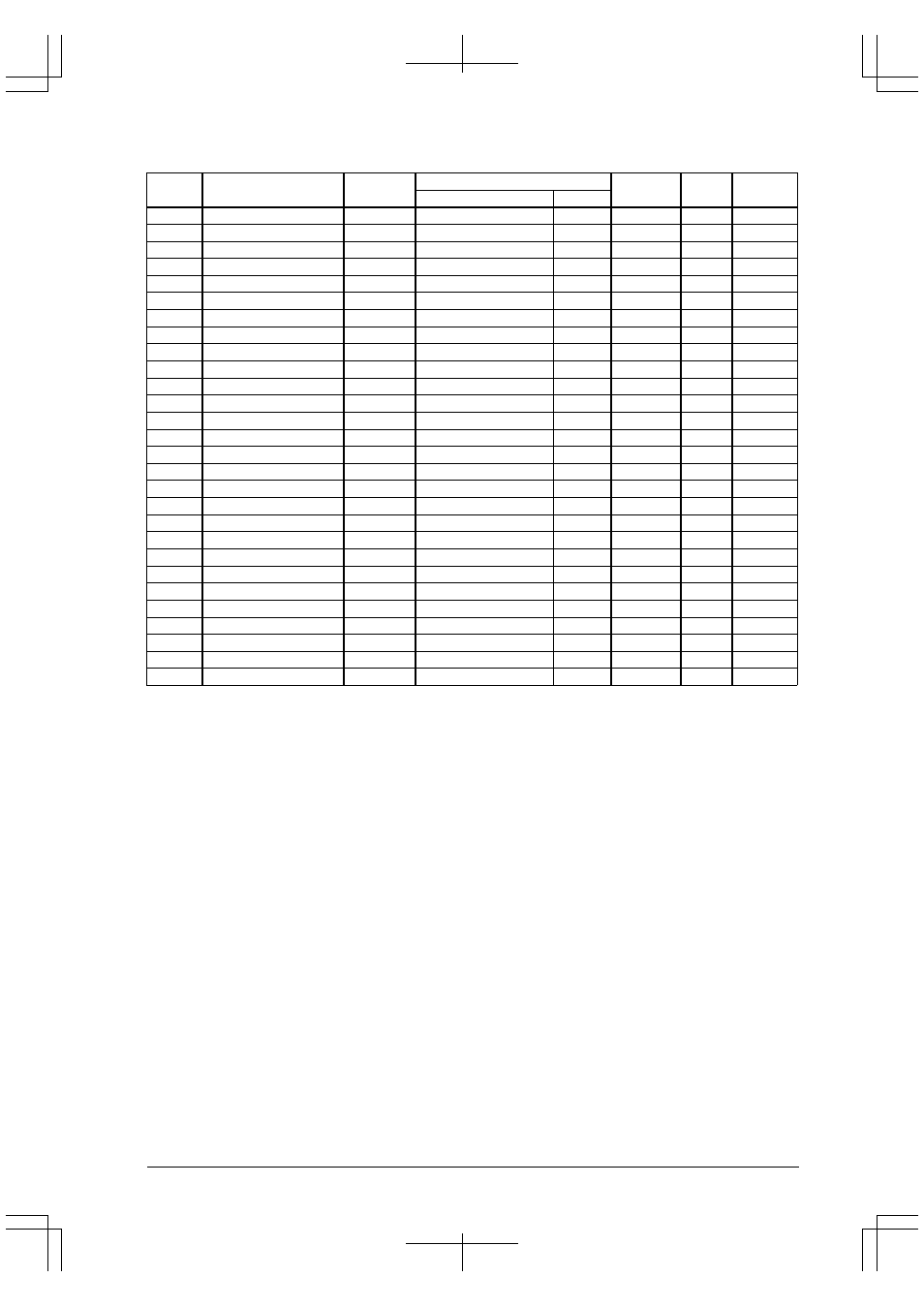

APPENDIX B PIN CHARACTERISTICS

S1C33210 PRODUCT PART

EPSON

A-109

Pin No.

Signal name

I/O cell

Characteristic

Pull-up/

Power

Remarks

name

Input

Output

down

supply

101

CTS

XIBC

CMOS/LVTTL

V

DD

102

V

SS

103

PLLC

XLIN

V

DD

104

V

SS

XIBCD1

CMOS/LVTTL

Pull-down

105

PLLS1

XIBC

CMOS/LVTTL

V

DD

106

PLLS0

XIBC

CMOS/LVTTL

V

DD

107

RXD/SIN3

XIBC

CMOS/LVTTL

V

DD

108

DCD

XIBC

CMOS/LVTTL

V

DD

109

MSEL

XIBCP2

Pull-up

V

DD

110

GOUT

XOB1T

CMOS/LVTTL

2 mA

V

DD

111

V

DD

112

OSC3

XLIN

V

DD

113

OSC4

XLOT

V

DD

114

EA10MD0

XIBC

CMOS/LVTTL

V

DD

115

EA10MD1

XIBCP2

CMOS/LVTTL

Pull-up

V

DD

116

#X2SPD

XIBC

CMOS/LVTTL

V

DD

117

P21/#DWE/#GAAS

XBH1T

CMOS/LVTTL SCHMITT

2 mA

V

DD

118

P22/TM0

XBH1T

CMOS/LVTTL SCHMITT

2 mA

V

DD

119

P23/TM1

XBH1T

CMOS/LVTTL SCHMITT

2 mA

V

DD

120

DSIO

XBH2P2T

CMOS/LVTTL SCHMITT

6 mA

Pull-up

V

DD

121

P10/EXCL0/T8UF0/DST0

XBH2T

CMOS/LVTTL SCHMITT

6 mA

V

DD

122

P11/EXCL1/T8UF1/DST1

XBH2T

CMOS/LVTTL SCHMITT

6 mA

V

DD

123

P12/EXCL2/T8UF2/DST2

XBH2T

CMOS/LVTTL SCHMITT

6 mA

V

DD

124

P13/EXCL3/T8UF3/DPC0

XBH2T

CMOS/LVTTL SCHMITT

6 mA

V

DD

125

P14/FOSC1/DCLK

XBH2T

CMOS/LVTTL SCHMITT

6 mA

V

DD

126

P24/TM2/#SRDY2

XBH1T

CMOS/LVTTL SCHMITT

2 mA

V

DD

127

P25/TM3/#SCLK2

XBH1T

CMOS/LVTTL SCHMITT

2 mA

V

DD

128

P15/EXCL4/#DMAEND0

XBH1T

CMOS/LVTTL SCHMITT

2 mA

V

DD

Note 1) The voltage applied to this pin must be 0V

≤

V

IN

≥

V

DD

.

Note 2) This pin is set as an input pin during device testing. Normally it is an output pin.

Note 3) The XBB1 cell is a fail-safe cell.