Epson S1C33210 User Manual

Page 134

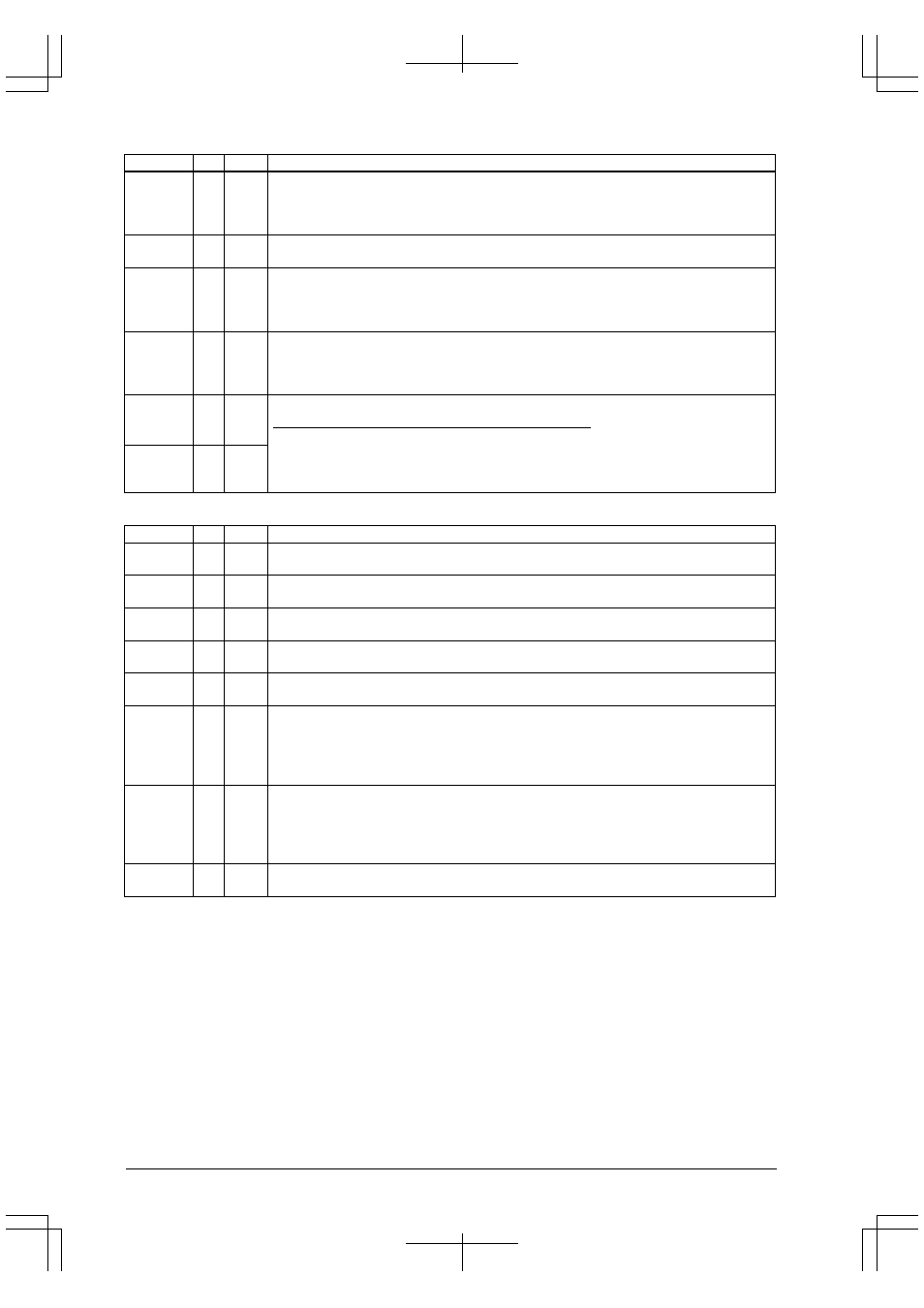

I OUTLINE: LIST OF PINS

B-I-3-2

EPSON

S1C33210 FUNCTION PART

Pin name

I/O

Pull-up

Function

P30

#WAIT

#CE4&5

I/O

–

P30: I/O

port

when

CFP30(D0/0x402DC)

=

"0"

(default)

#WAIT:

Wait cycle request input when CFP30(D0/0x402DC) = "1"

#CE4&5: Areas

4&5

chip

enable

when

CFP30(D0/0x402DC)

=

"1"

and

IOC30(D0/0x402DE) = "1"

P20

#DRD

I/O

–

P20:

I/O port when CFP20(D0/0x402D8) = "0" (default)

#DRD:

DRAM read signal output for successive RAS mode when CFP20(D0/0x402D8) = "1"

P21

#DWE

#GAAS

I/O

–

P21:

I/O port when CFP21(D1/0x402D8) = "0" and CFEX2(D2/0x402DF) = "0" (default)

#DWE: DRAM

read

signal

output

for

successive

RAS

mode

when

CFP21(D1/0x402D8)

=

"1"

and

CFEX2(D2/0x402DF) = "0"

#GAAS: Area

address

strobe

for

GA

when

CFEX2(D2/0x402DF)

=

"1"

P31

#BUSGET

#GARD

I/O

–

P31:

I/O port when CFP31(D1/0x402DC) = "0" and CFEX3(D3/0x402DF) = "0" (default)

#BUSGET: Bus status monitor signal output when CFP31(D1/0x402DC) = "1" and CFEX3(D3/0x402DF)

= "0"

#GARD: Area

read

signal

output

for

GA

when

CFEX3(D3/0x402DF)

=

"1"

EA10MD1

I

Pull-up Area 10 boot mode selection

EA10MD1

EA10MD0

Mode

1

1

External ROM mode

EA10MD0

I

–

1

0

–

0

1

–

0

0

–

Table 3.2 List of Pins for HSDMA Control Signals

Pin name

I/O

Pull-up

Function

K50

#DMAREQ0

I

Pull-up K50:

Input port when CFK50(D0/0x402C0) = "0" (default)

#DMAREQ0: HSDMA Ch. 0 request input when CFK50(D0/0x402C0) = "1"

K51

#DMAREQ1

I

Pull-up K51:

Input port when CFK51(D1/0x402C0) = "0" (default)

#DMAREQ1: HSDMA Ch. 1 request input when CFK51(D1/0x402C0) = "1"

P32

#DMAACK0

I/O

–

P32:

I/O port when CFP32(D2/0x402DC) = "0" (default)

#DMAACK0: HSDMA Ch. 0 acknowledge output when CFP32(D2/0x402DC) = "1"

P33

#DMAACK1

I/O

–

P33:

I/O port when CFP33(D3/0x402DC) = "0" (default)

#DMAACK1: HSDMA Ch. 1 acknowledge output when CFP33(D3/0x402DC) = "1"

P04

SIN1

I/O

–

P04:

I/O port when CFP04(D4/0x402D0) = "0" and CFEX4(D4/0x402DF) = "0" (default)

SIN1:

Serial I/F Ch. 1 data input when CFP04(D4/0x402D0) = "1" and CFEX4(D4/0x402DF) = "0"

P15

EXCL4

#DMAEND0

I/O

–

P15:

I/O port when CFP15(D5/0x402D4) = "0" (default)

EXCL4:

16-bit timer 4 event counter input when CFP15(D5/0x402D4) = "1" and IOC15(D5/0x402D6)

= "0"

#DMAEND0: HSDMA Ch. 0 end-of-transfer signal output when CFP15(D5/0x402D4) = "1" and

IOC15(D5/0x402D6) = "1"

P16

EXCL5

#DMAEND1

I/O

–

P16:

I/O port when CFP16(D6/0x402D4) = "0" (default)

EXCL5:

16-bit timer 5 event counter input when CFP16(D6/0x402D4) = "1" and IOC16(D6/0x402D6)

= "0"

#DMAEND1: HSDMA Ch. 1 end-of-transfer signal output when CFP16(D6/0x402D4) = "1" and

IOC16(D6/0x402D6) = "1"

P05

SOUT1

I/O

–

P05:

I/O port when CFP05(D5/0x402D0) = "0" and CFEX5(D5/0x402DF) = "0" (default)

SOUT1:

Serial I/F Ch. 1 data output when CFP05(D5/0x402D0) = "1" and CFEX5(D5/0x402DF) = "0"