Epson S1C33210 User Manual

Page 215

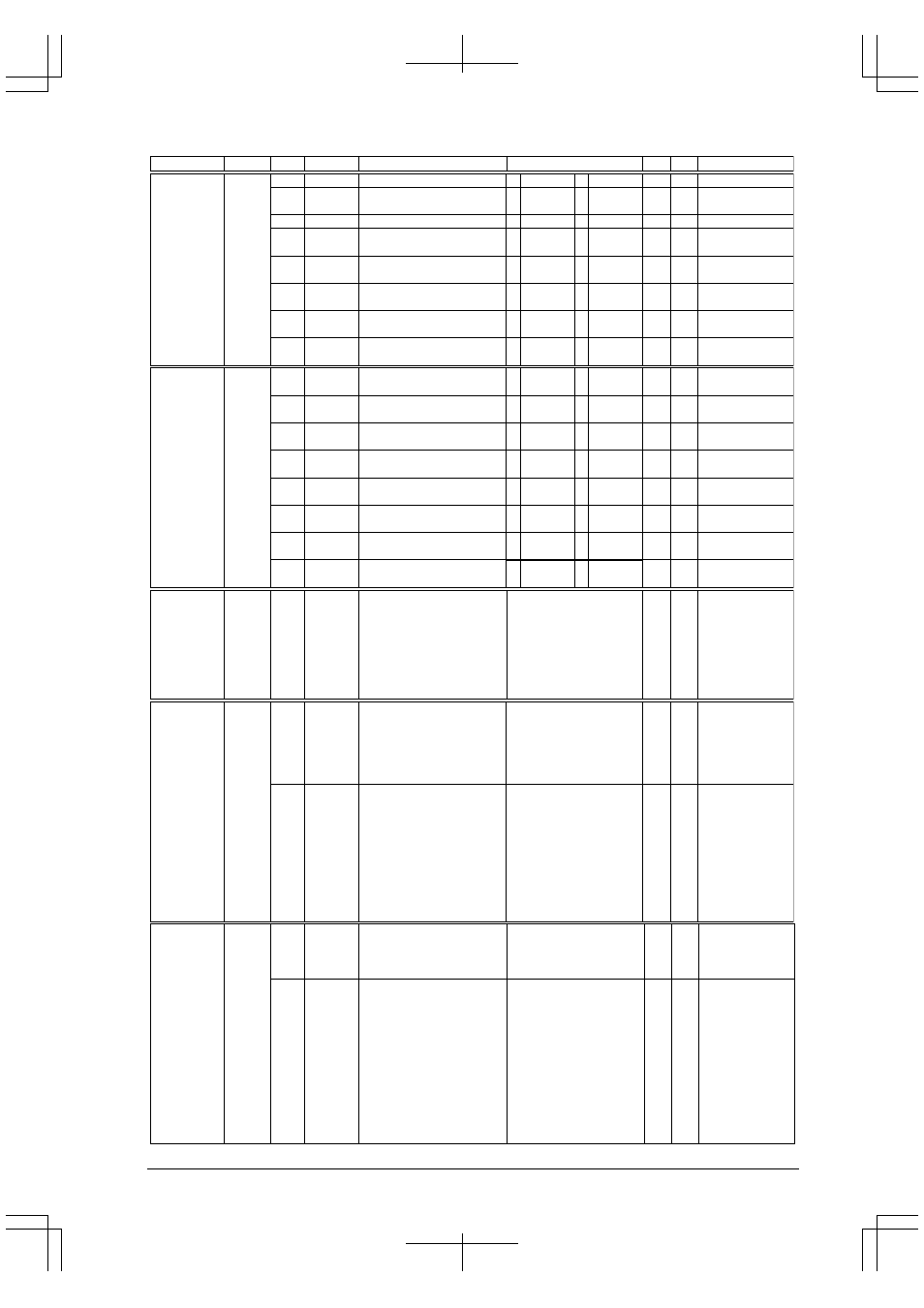

II CORE BLOCK: ITC (Interrupt Controller)

S1C33210 FUNCTION PART

EPSON

B-II-5-17

Name

Address

Register name

Bit

Function

Setting

Init.

R/W

Remarks

T8CH5S0

SIO3TS0

T8CH4S0

SIO3RS0

SIO2TS0

SIO3ES0

SIO2RS0

SIO2ES0

D7

D6

D5

D4

D3

D2

D1

D0

8-bit timer 5 underflow

SIO Ch.3 transmit buffer empty

8-bit timer 4 underflow

SIO Ch.3 receive buffer full

SIO Ch.2 transmit buffer empty

SIO Ch.3 receive error

SIO Ch.2 receive buffer full

SIO Ch.2 receive error

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

00402C5

Interrupt factor

FP function

switching

register

1 SIO Ch.3

TXD Emp.

0 FP6

1 SIO Ch.3

RXD Full

0 FP4

1 SIO Ch.2

TXD Emp.

0 FP3

1 SIO Ch.3

RXD Err.

0 FP2

1 SIO Ch.2

RXD Full

0 FP1

1 SIO Ch.2

RXD Err.

0 FP0

1 T8 Ch.5 UF 0 FP7

1 T8 Ch.4 UF 0 FP5

T8CH5S1

T8CH4S1

SIO3ES1

SIO2ES1

SIO3TS1

SIO3RS1

SIO2TS1

SIO2RS1

D7

D6

D5

D4

D3

D2

D1

D0

8-bit timer 5 underflow

8-bit timer 4 underflow

SIO Ch.3 receive error

SIO Ch.2 receive error

SIO Ch.3 transmit buffer empty

SIO Ch.3 receive buffer full

SIO Ch.2 transmit buffer empty

SIO Ch.2 receive buffer full

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

00402CB

Interrupt factor

TM16 function

switching

register

1 SIO Ch.3

RXD Err.

0 TM16 Ch.3

comp.A

1 SIO Ch.2

RXD Err.

0 TM16 Ch.3

comp.B

1 SIO Ch.3

TXD Emp.

0 TM16 Ch.4

comp.A

1 SIO Ch.3

RXD Full

0 TM16 Ch.4

comp.B

1 SIO Ch.2

TXD Emp.

0 TM16 Ch.5

comp.A

1 SIO Ch.2

RXD Full

0 TM16 Ch.5

comp.B

1 T8 Ch.5 UF 0 TM16 Ch.2

comp.A

1 T8 Ch.4 UF 0 TM16 Ch.2

comp.B

TBRP7

TBRP6

TBRP5

TBRP4

TBRP3

TBRP2

TBRP1

TBRP0

D7

D6

D5

D4

D3

D2

D1

D0

TTBR register write protect

0

0

0

0

0

0

0

0

W

Undefined in read.

004812D

(B)

Writing 01011001(0x59)

removes the TTBR (0x48134)

write protection.

Writing other data sets the

write protection.

TTBR write

protect register

TTBR15

TTBR14

TTBR13

TTBR12

TTBR11

TTBR10

TTBR09

TTBR08

TTBR07

TTBR06

TTBR05

TTBR04

TTBR03

TTBR02

TTBR01

TTBR00

DF

DE

DD

DC

DB

DA

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

Trap table base address [15:10]

Trap table base address [9:0]

Fixed at 0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

R/W

R

0 when being read.

Writing 1 not allowed.

0048134

(HW)

TTBR low-

order register

TTBR33

TTBR32

TTBR31

TTBR30

TTBR2B

TTBR2A

TTBR29

TTBR28

TTBR27

TTBR26

TTBR25

TTBR24

TTBR23

TTBR22

TTBR21

TTBR20

DF

DE

DD

DC

DB

DA

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

Trap table base address [31:28]

Trap table base address [27:16]

Fixed at 0

0x0C0

0

0

0

0

0

0

0

0

1

1

0

0

0

0

0

0

R

R/W

0 when being read.

Writing 1 not allowed.

0048136

(HW)

TTBR high-

order register