Ds4830 user’s guide – Maxim Integrated DS4830 Optical Microcontroller User Manual

Page 87

DS4830 User’s Guide

87

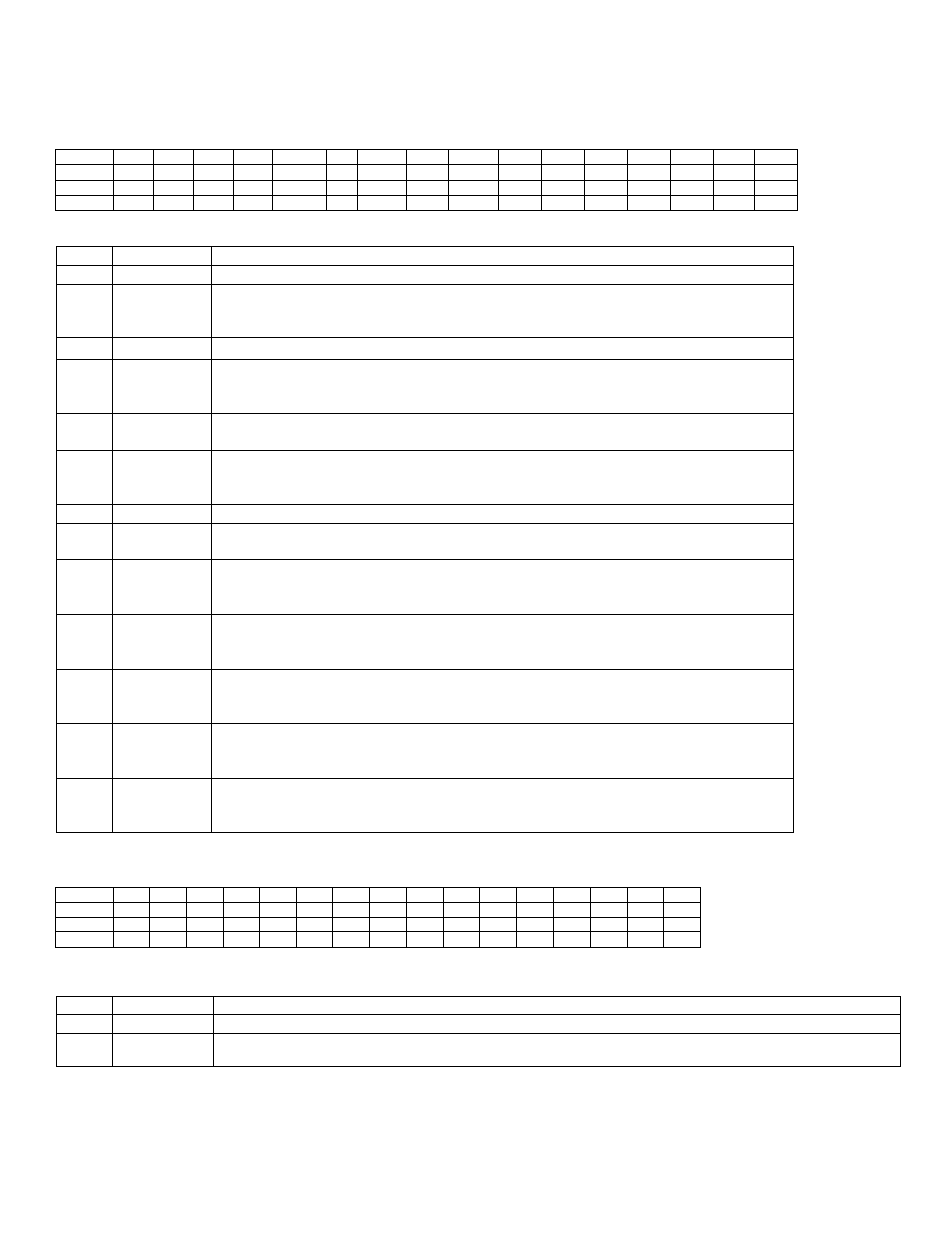

10.2.3

– I

2

C Master Interrupt Enable Register (I2CIE_M)

Address: M1[02h]

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

-

-

-

-

I2CSPIE

-

I2CROIE I2CGCIE I2CNACKIE

-

I2CAMIE I2CTOIE I2CSTRIE I2CRXIE I2CTXIE I2CSRIE

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

r

r

r

r

rw

r

rw

rw

rw

r

rw

rw

rw

rw

rw

rw

BIT

NAME

DESCRIPTION

15:12 Reserved

Reserved. The user should write 0 to these bits.

11

I2CSPIE

I

2

C Master STOP Interrupt Enable.

Setting this bit to ‘1’ will enable an interrupt

when a STOP condition

is detected (I2CSPI=1). Clearing this bit to ‘0’ will disable

the STOP detection interrupt.

10

Reserved

Reserved. The user should not write to this bit.

9

I2CROIE

I

2

C Master Receiver Overrun Interrupt Enable. Setting this bit to

‘1’ will enable

an interrupt when a receiver overrun condition is detected (I2ROI=1). Clearing this

bit to

‘0’ will disable the receiver overrun detection interrupt.

8

I2CGCIE

I

2

C General Call Interrupt Enable. This bit has no function when operating in

master mode.

7

I2CNACKIE I

2

C Master NACK Interrupt Enable. Setting this bit to

‘1’ will enable an interrupt

when a NACK is detected (I2CNACKI=1). Clearing this bit to

‘0’ will disable the

NACK detection interrupt.

6

Reserved

Reserved. The user should write 0 to this bit.

5

I2CAMIE

I

2

C Address Match Interrupt Enable. This bit has no function when operating in

master mode.

4

I2CTOIE

I

2

C Master Timeout Interrupt Enable. Setting this bit to

‘1’ will enable an

interrupt when a timeout condition is detected (I2CTOI=1). Clearing this bit to

‘0’

will disable the timeout interrupt.

3

I2CSTRIE

I

2

C Master Clock Stretch Interrupt Enable. Setting this bit to

‘1’ will enable an

interrupt when the clock stretch interrupt flag is set (I2CSTRI=1). Clearing this bit

will disable the clock stretch interrupt.

2

I2CRXIE

I

2

C Master Receive Ready Interrupt Enable. Setting this bit to

‘1’ will enable an

interrupt when receive ready interrupt flag is set (I2CRXI=1). Clearing this bit to

‘0’

will disable the receive ready interrupt.

1

I2CTXIE

I

2

C Master Transmit Complete Interrupt Enable. Setting this bit to

‘1’ will enable

an interrupt when transmit complete interrupt flag is set (I2CTXI=1). Clearing this

bit to

‘0’ disables transmit complete interrupt.

0

I2CSRIE

I

2

C Master START Interrupt Enable. Setting this bit to

‘1’ will enable an interrupt

when a START condition is detected (I2CSRI=1). Clearing this bit to

‘0’ will

disable the START detection interrupt.

10.2.4

– I

2

C Master Data Buffer Register (I2CBUF_M)

Address: M1[00h]

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

-

-

-

-

-

-

-

-

D7

D6

D5

D4

D3

D2

D1

D0

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

rw*

rw*

rw*

rw*

rw*

rw*

rw*

rw*

* Unrestricted read access. This register can be written to only when I2CBUSY = 0.

BIT

NAME

DESCRIPTION

15:8

Reserved

Reserved. The user should write 0 to these bits.

7:0

D[7:0]

Data for I

2

C transfer is read from or written to this location. The I

2

C transmit and receive buffers are

separate but both are addressed at this location.