Ds4830 user’s guide – Maxim Integrated DS4830 Optical Microcontroller User Manual

Page 25

DS4830 User’s Guide

25

3.1 Accumulator Pointer Register (AP, 8h[0h])

Initialization: This register is cleared to 00h on all forms of reset.

Access: Unrestricted direct read/write access.

Bit

Name

Function

7:4

Reserved

Reserved. All reads return 0.

3:0

AP[3:0]

Active Accumulator Select. These bits select which of the 16 accumulator registers are used for arithmetic and logical

operations. If the APC register has been set to perform automatic increment/decrement of the active accumulator, this setting

will be automatically changed after each arithmetic or logical operation. I

f a ‘MOVE AP, Acc’ instruction is executed, any enabled

AP inc/dec/modulo control will take precedence over the transfer of Acc data into AP.

3.2 Accumulator Pointer Control Register (APC, 8h[1h])

Initialization: This register is cleared to 00h on all forms of reset.

Access: Unrestricted direct read/write access.

Bit

Name

Function

7

CLR

AP Clear. Writing this bit to 1 clears the accumulator pointer AP to 0. Once set, this bit will automatically be reset to 0 by

hardware. If a ‘MOVE APC, Acc’ instruction is executed requesting that AP be set to 0 (i.e., CLR = 1), the AP clear function

overrides any enabled inc/dec/modulo control. All reads from this bit return 0.

6

IDS

Increment/Decrement Select. If this bit is set to 0, the accumulator pointer AP is incremented following each arithmetic or logical

operation according to MOD[2:0]. If this bit is set to 1, the accumulator pointer AP is decremented following each arithmetic or

logical operation according to MOD[2:0]. If MOD[2:0] is set to 000, the setting of this bit is ignored.

5:3

Reserved

Reserved. All reads return 0.

2:0

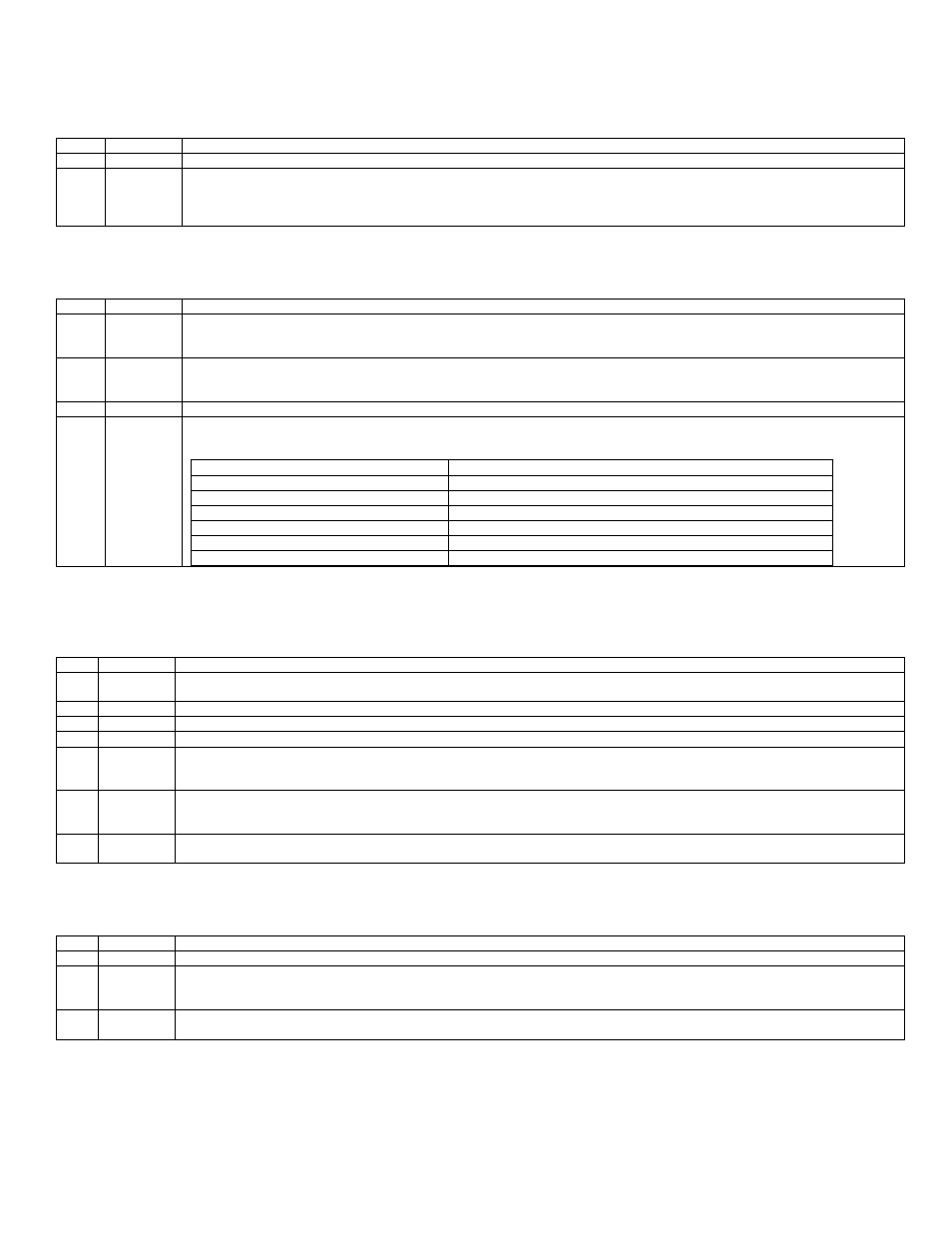

MOD[2:0]

Accumulator Pointer Auto Increment/Decrement Modulus. If these bits are set to a nonzero value, the accumulator pointer

(AP[3:0]) will be automatically incremented or decremented following each arithmetic or logical operation. The mode for the

auto-increment/ decrement is determined as follows:

MOD[2:0]

AUTO INCREMENT/DECREMENT MODE

000

No auto-increment/decrement (default)

001

Increment/decrement AP[0] modulo 2

010

Increment/decrement AP[1:0] modulo 4

011

Increment/decrement AP[2:0] modulo 8

100

Increment/decrement AP modulo 16

101 to 111

Reserved (modulo 16 when set)

3.3 Processor Status Flags Register (PSF, 8h[4h])

Initialization: This register is cleared to 80h on all forms of reset.

Access: Bit 7 (Z), bit 6 (S), and bit 2 (OV) are read only. Bits [4:3] (GPF[1:0]), bit 1 (C), and bit 0 (E) are unrestricted

read/write.

Bit

Name

Function

7

Z

Zero Flag. The value of this bit flag equals 1 whenever the active accumulator is equal to zero. This bit equals 0 if the active

accumulator is not equal to 0.

6

S

Sign Flag. This bit flag mirrors the current value of the high bit of the active accumulator (Acc.15).

5

Reserved

Reserved. All reads return 0.

4:3

GPF[1:0]

General-Purpose Flags. These general-purpose flag bits are provided for user software control.

2

OV

Overflow Flag. This flag is set to 1 if there is a carry out of bit 14 but not out of bit 15, or a carry out of bit 15 but not out of bit 14

from the last arithmetic operation, otherwise, the OV flag remains as 0. OV indicates a negative number resulted as the sum of

two positive operands, or a positive sum resulted from two negative operands.

1

C

Carry Flag. This bit flag is set to 1 whenever an add or subtract operation (ADD, ADDC, SUB, SUBB) returns a carry or borrow.

This bit flag is cleared to 0 whenever an add or subtract operation does not return a carry or borrow. Many other instructions

potentially affect the carry bit. Reference the instruction set documentation for details.

0

E

Equals Flag. This bit flag is set to 1 whenever a compare operation (CMP) returns an equal result. If a CMP operation returns not

equal, this bit is cleared.

3.4 Interrupt and Control Register (IC, 8h[5h])

Initialization: This register is cleared to 00h on all forms of reset.

Access: Unrestricted direct read/write access.

Bit

Name

Function

7:2

Reserved

Reserved. All reads return 0.

1

INS

Interrupt In Service. The INS is set by hardware automatically when an interrupt is acknowledged. No further interrupts occur as

long as the INS remains set. The interrupt service routine can clear the INS bit to allow interrupt nesting. Otherwise, the INS bit is

cleared by hardware upon execution of an RETI or POPI instruction.

0

IGE

Interrupt Global Enable. If this bit is set to 1, interrupts are globally enabled, but still must be locally enabled to occur. If this bit is

set to 0, all interrupts are disabled.