2 – module interrupt identification registers, Module interrupt identification registers, Ds4830 user’s guide – Maxim Integrated DS4830 Optical Microcontroller User Manual

Page 39

DS4830 User’s Guide

39

pending interrupt. The peripheral register bits inside the module also provide a way to differentiate among interrupt

sources. Section 5.2 has more detail on the Module Interrupt Identification Registers.

The Interrupt Vector (IV) register provides the location of the interrupt service routine. It may be set to any location within

program memory. The IV register defaults to 0000h on reset or power-up, so if it is not changed to a different address, the

user program must determine whether a jump to 0000h came from a reset or interrupt source.

5.2

– Module Interrupt Identification Registers

The MIIR registers are implemented to indicate which particular function within a peripheral module has caused the

interrupt. The DS4830 has 6 peripheral modules, M0 through M5. MIIR registers are implemented in peripheral module 1

and 2. The MIIR registers are 16-bit read-only registers and all of them default to 0000h on system reset.

Each defined bit in an MIIR register is the final interrupt from a specific function, i.e., the interrupt enable bit(s) AND-ed

with the interrupt flag(s). A function can have multiple flags but they all are AND-ed with corresponding enable bits and

combined to create a single interrupt identification bit for that specific function. For example, the I

2

C master has several

interrupt sources; however, they all are combined to form a single identification bit, MIIR1.I2CM. The individual register bit

functions are defined as follows.

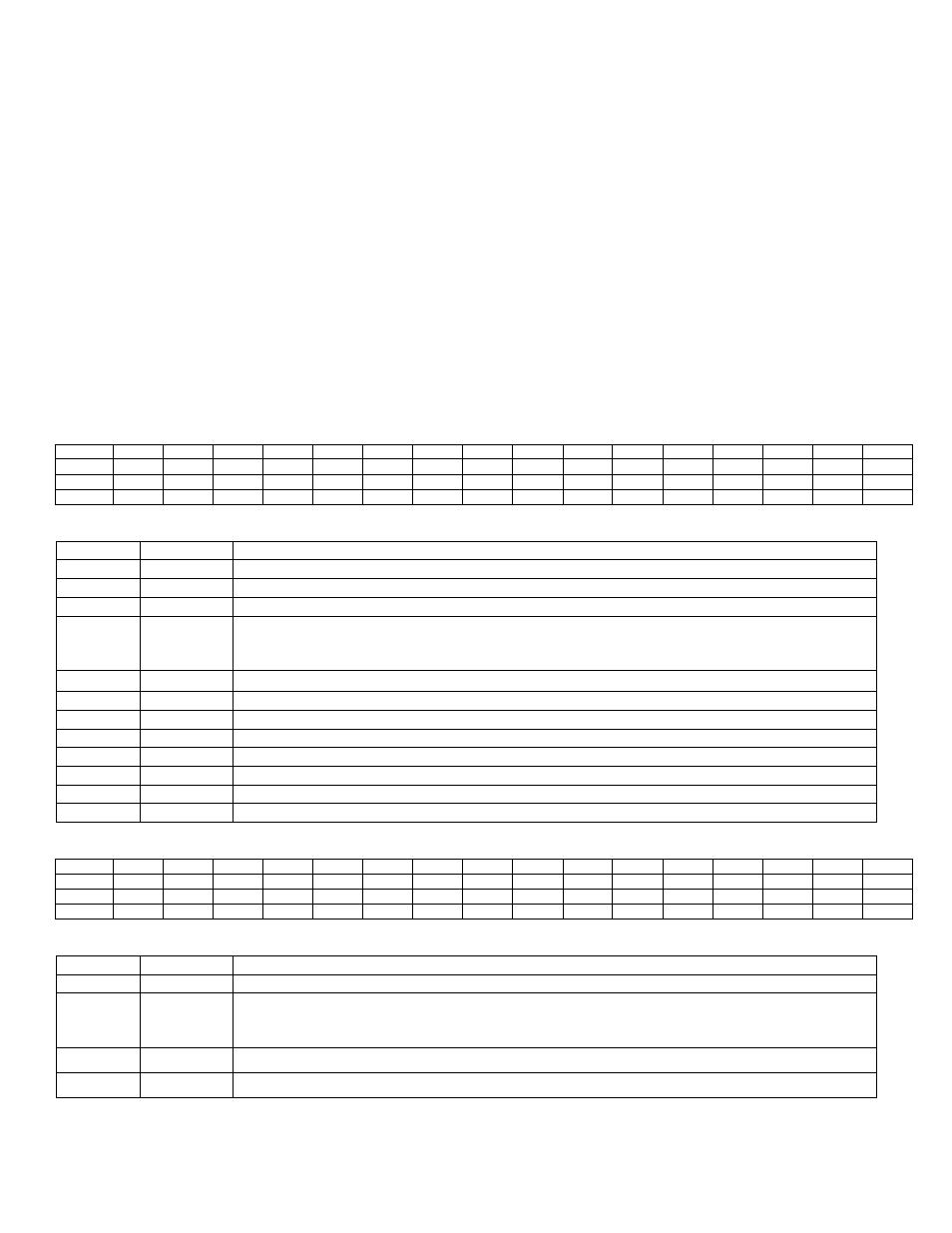

Peripheral Module 1 Interrupt Identification Register (MIIR1, M1[04h])

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Reserved Reserved Reserved Reserved Reserved

SPI_S

Reserved

I2CM

SVM

P6_6

P6_5

P6_4

P6_3

P6_2

P6_1

P6_0

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r

BIT

NAME

DESCRIPTION

15:11

Reserved

Reserved. A read returns 0.

10

SPI_S

This bit is set when there is an interrupt at SPI Slave.

9

Reserved

Reserved. A read returns 0.

8

I2CM

This bit is set when there is an interrupt from the I

2

C master block. The I

2

C interrupt is a

combination of all interrupts defined in the I2CST_M register for the I

2

C master block. The

Master I

2

C section has more detail on the individual interrupts.

7

SVM

This bit is set when there is an interrupt from Supply Voltage Monitor (SVM).

6

P6_6

This bit is set when there is an External GPIO Interrupt at P6.6.

5

P6_5

This bit is set when there is an External Interrupt at P6_5.

4

P6_4

This bit is set when there is an External Interrupt at P6.4.

3

P6_3

This bit is set when there is an External Interrupt at P6.3.

2

P6_2

This bit is set when there is an External Interrupt at P6.2.

1

P6_1

This bit is set when there is an External Interrupt at P6.1.

0

P6_0

This bit is set when there is an External Interrupt at P6.0.

Peripheral Module 2 Interrupt Identification Register (MIIR2, M2[03h])

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved

I2CS

ADC

TW

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r

BIT

NAME

DESCRIPTION

15:3

Reserved

Reserved. A read returns 0.

2

I2CS

This bit is set when there is an interrupt from the I

2

C slave block. The I

2

C interrupt is a

combination of all interrupts defined in the I2CST_S register for the I

2

C slave block. The

Slave I

2

C section has more detail on the individual interrupts.

1

ADC

This bit is set when there is an Interrupt from the ADC.

0

TW

This bit is set when there is an interrupt from the 3Wire Block.