6 – generating a stop, Generating a stop, Ds4830 user’s guide – Maxim Integrated DS4830 Optical Microcontroller User Manual

Page 79

DS4830 User’s Guide

79

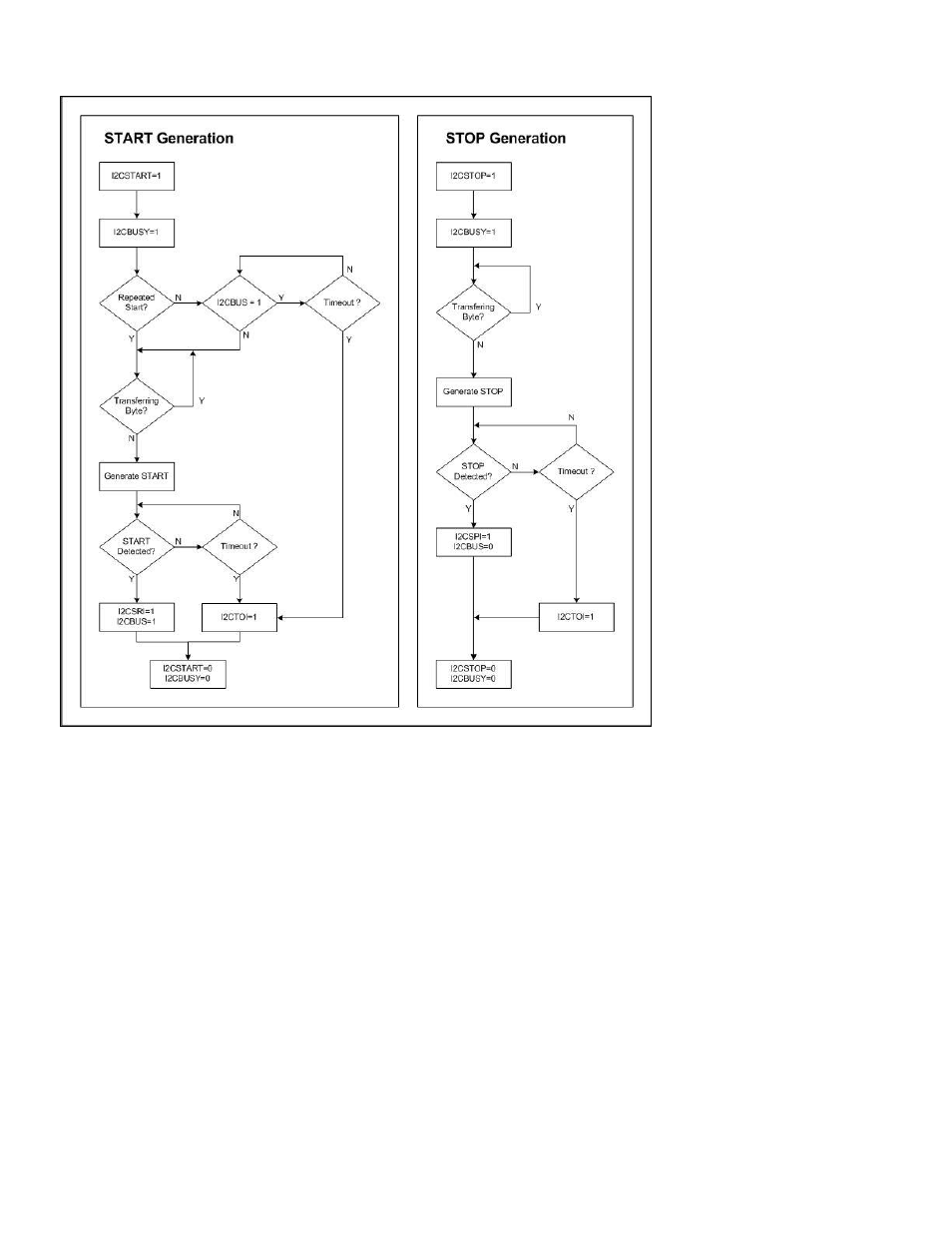

Figure 10-3: Master I

2

C Generated START and STOP

10.1.6

– Generating a STOP

To end an I

2

C transfer, a STOP must be transmitted. A STOP is generated by setting the I2CSTOP bit. The master

I

2

C

controller’s flow when attempting to issue a STOP command is shown in Figure 10-3.

If the I2CSTOP bit is set when the I

2

C Controller is in the middle of a byte transfer (after the 1

st

bit rising edge), it will wait for

the current byte transfer to finish (after the 9

th

bit) before generating the STOP condition.

Because the SDA line is feedback into the device, when the master generates a STOP, it will also detect the STOP

condition. When a STOP condition is detected, the I

2

C STOP interrupt flag (I2CSPI) will be set and an interrupt will be

generated enabled. The I2CBUS bit will be cleared to indicate that the I

2

C bus is now idle and the I2CSTOP bit will be

cleared.

When the master I

2

C controller attempts to generate the STOP condition, it will also start the timeout timer if this feature is

enabled. If a timeout is generated before the STOP condition is detected, a timeout will occur. When a timeout occurs,

the I2CTOI bit will be set, which can generate an interrupt if enabled, and the I2CSTOP bit will also be cleared to 0.