Section 22 – in-system programming, 1 – detailed description, Section 22 – Maxim Integrated DS4830 Optical Microcontroller User Manual

Page 169: In-system programming, Detailed description, Ds4830 user’s guide

DS4830 User’s Guide

169

SECTION 22

– IN-SYSTEM PROGRAMMING

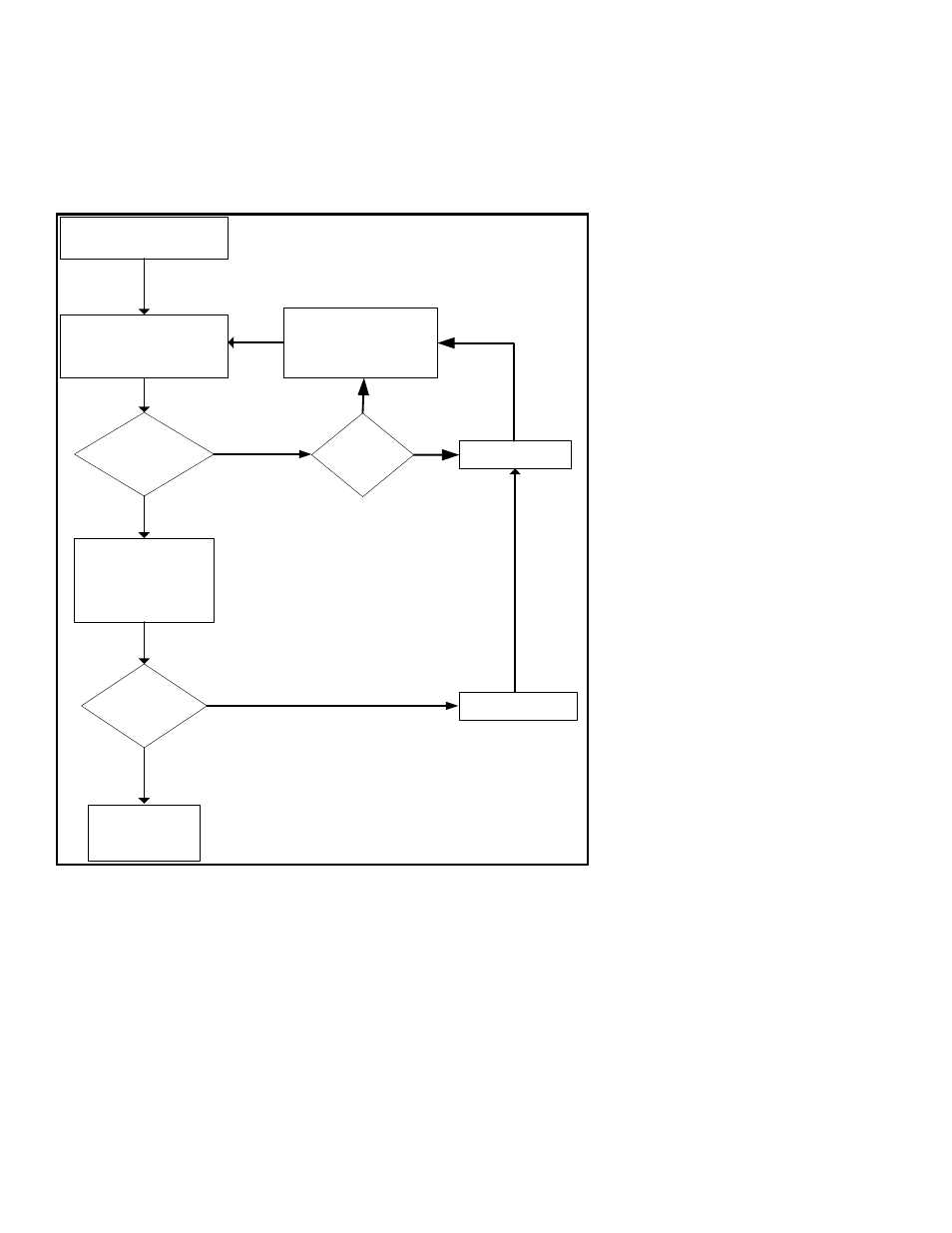

The DS4830 contains an internal bootstrap loader utilizing the JTAG or I

2

C interfaces. As a result, system software can

be upgraded in-system, eliminating the need for a costly hardware retrofit when software updates are required. After each

device reset, DS4830 ROM code is executed which determines if bootloader operation is desired. Figure 22-1 provides

information on how the DS4830 enters into bootloader operation.

Any Device Reset Occurs

Reset Device.

Begin Boot ROM code

execution at

8000h.

ROM Code enable the

Slave I

2

C Interface

Is JTAG_SPE

bit set?

Is I2C_SPE

bit set?

Jump to user

code

(flash) at 0000h,

Set PSS{1:0] = 01

Bootloader

Exit Bootloader

Delay 320 Clock Cycles

Set PWL and ROD bits.

Yes

No

Yes

No

Is PSS[1:0]

!= 1X

Exit Loader

Command

Yes

No

Figure 22-1: Entering Bootloader Operation

22.1

– Detailed Description

Following every reset, device ROM code is executed which determines if the DS4830 should enter into a bootloader

mode. First, the ICDF register, which is not cleared by a reset, is read to see if the System Programming Enable (SPE)

bit is set. See the Entering JTAG Bootload section for more details on setting the SPE bit. If SPE is set, the DS4830 will

enter into bootloader operation.

If SPE is not set, the DS4830 then enables the slave I

2

C interface. The I2C_SPE bit in the I2C_SPB register is read to

determine if I

2

C bootloader operation is desired. The I2C_SPB register is not cleared by a reset. See the Entering I

2

C

Bootload section for more details on setting the I2C_SPE bit. If I2C_SPE is set, the DS4830 will set the PSS[1:0] bits to

01, which designates I

2

C bootloader, and enter bootloader operation.