Ds4830 user’s guide – Maxim Integrated DS4830 Optical Microcontroller User Manual

Page 104

DS4830 User’s Guide

104

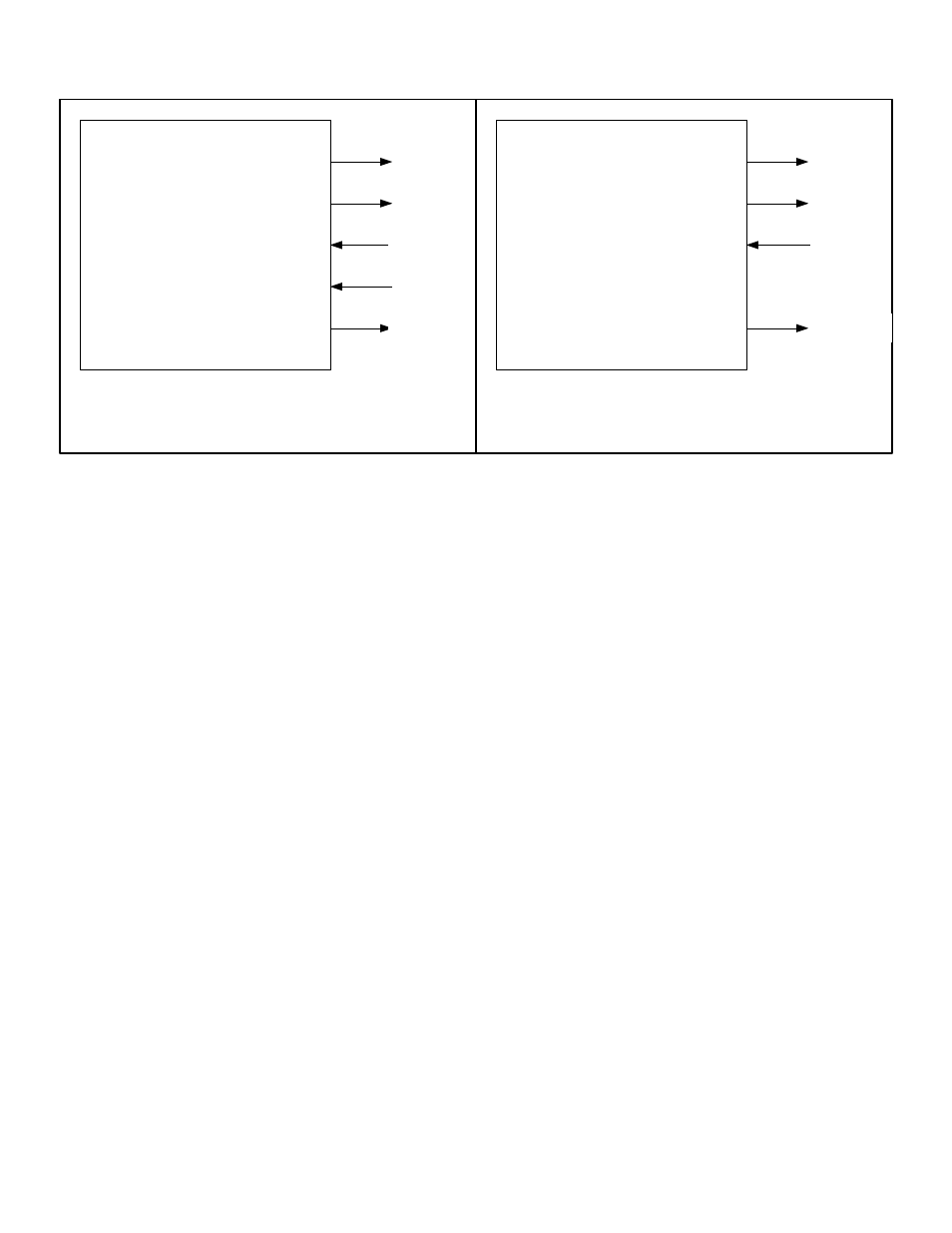

Figure 12-4

:

SPI Master Pin Configurations

with mode fault enable and disable

In master mode, the MSPICS pin of the master defaults to general-purpose I/O pin. However, as shown in Figure 12-4 the

MSPICS can be used for mode fault detection input if the Mode Fault Enable bit (MODFE) is set. When the SPI is

configured as a master and the MSPICS pin is used as mode fault detection input, a mode fault condition occurs if an

active signal is detected on MSPICS. This indicates that some other device on the network is attempting to be a master.

The active signal is defined by the Slave Active Select (SAS) bit. When MODFE is set to 1 and SAS is cleared to 0, an

active low signal on MSPICS will trigger a mode fault. If MODFE is set to 1 and SAS is set to 1, an active high signal on

MSPICS will indicate a mode fault condition. Either way, the master device will sense the error and immediately disables

the SPI device to avoid potentially damaging bus contentions.

To avoid unintentional mode fault error, prior to enabling the SPI peripheral as master with mode fault enabled, software

should check the status of MSPICS. MSPICS should be held inactive for at least 2 system clocks before enabling the SPI

master. Otherwise, mode fault will occur and the SPI MSTM bit will be cleared to 0 and the SPI disabled.

SPI Master

MSPICK

MSPIDO

MSPIDI

MSPICS

CS

(Any GPIO)

SPI Master

CS

(Any GPIO)

Mode Fault Enable

CS: External Slave Chip Select

Mode Fault Disable

Note: MSPICS can be used as CS for External Slave Device

MSPICK

MSPIDO

MSPIDI