9 – adc interrupts, 10 – adc internal offset, Adc interrupts – Maxim Integrated DS4830 Optical Microcontroller User Manual

Page 51: Adc internal offset, Ds4830 user’s guide

DS4830 User’s Guide

51

location configured in the ALT_LOC[4:0] bits in the ADDATA during ADC configuration (ADST.ADCFG = 1). This buffer is

accessed by reading the ADDATA register when ADCFG is set to 0. The data buffer pointed to by ADST.ADIDX [4:0] will

be the buffer returned when ADDATA is read. The ADIDX is automatically incremented following a read of ADDATA.

This allows repeated reads of ADDATA to return the results from multiple conversions. The ADC will continue writing to

the data buffer until the end of the buffer. Once the end of the data buffer is reached, the ADC index will rollover and write

to data buffer 0.

7.1.9

– ADC Interrupts

The ADC Data Available Ready ADDAI in the ADST register will be set when conversions are complete. This flag will

generate an interrupt if enabled by setting the ADCN.ADDAIE interrupt enable bit. The condition that causes the ADDAI

flag to be set can be selected using the ADCN.ADDAINV bit.

Table 7-3. ADC Interrupt Intervals

ADDAINV

Set ADDAI after

0

End of Every Sequence (ADSTART to ADEND)

1

After End of Every Sequence (ADSTART to ADEND) and After

(NUM_SMP + 1) ADC Conversions

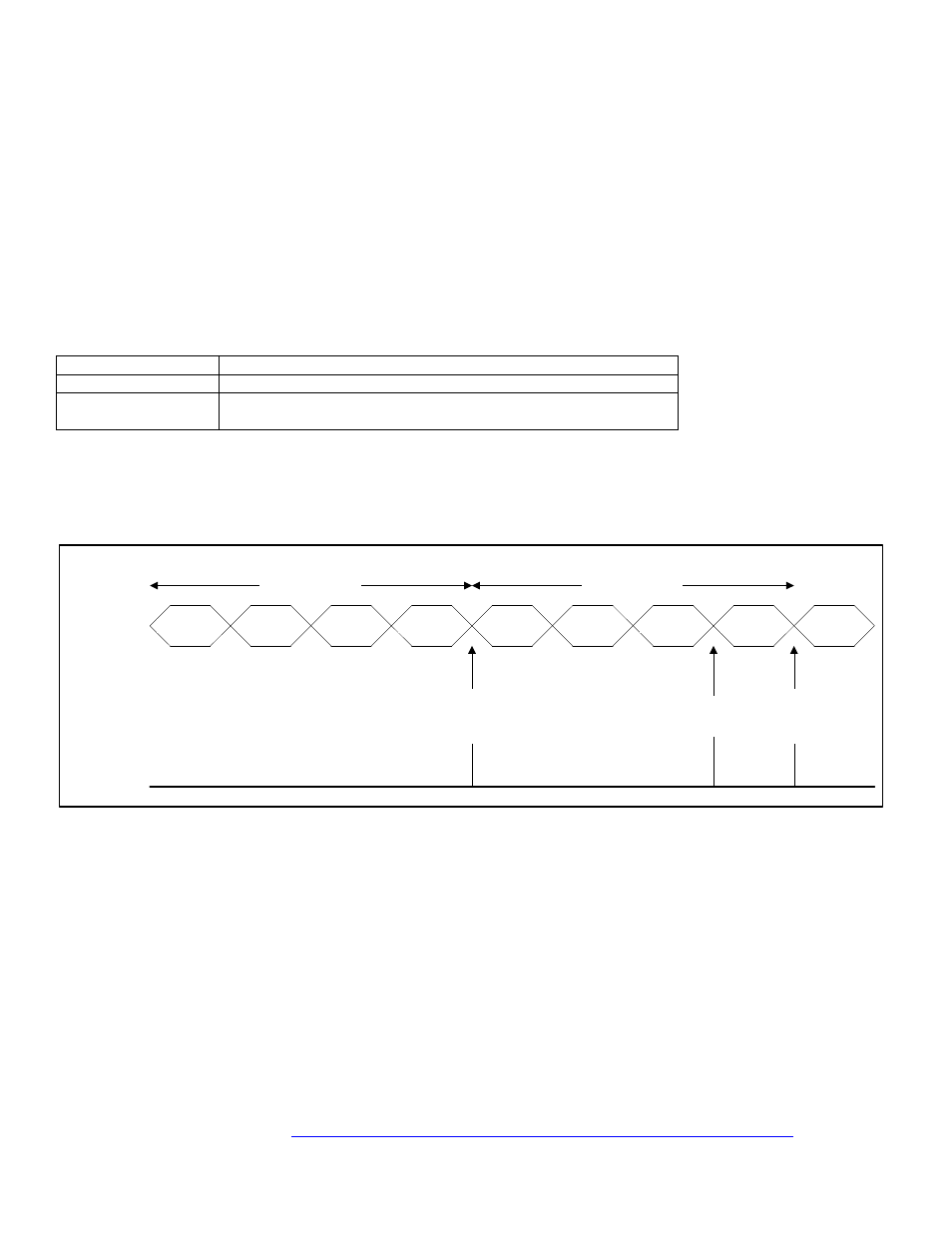

For example, if ADSTART = 0, ADEND = 6 and NUM_SMP = 3 with ADDAINV = 1, then

ADDAI will be set to ‘1’ after

every (NUM_SMP + 1) ADC conversions and every End of Sequence. In the given example, ADDAI will be set after

4,7,8,12,14… ADC Samples. Interrupts after 4, 8 and 12 ADC Samples are because of (NUM_SMP+1) configurations and

interrupts after 7 and 14 are because o

f “End of Sequence”. Figure 7-5 demonstrates above ADC example sequence.

SAMPLE1

SAMPLE2

SAMPLE3

SAMPLE4

SAMPLE5

SAMPLE6

SAMPLE7

SAMPLE8

……...

ADDAI Set

After

(NUM_SMP + 1)

ADC Samples

ADDAI Set

After END of

Sequence

4 ADC Samples

4 ADC Samples

ADDAI Set

After

(NUM_SMP + 1)

ADC Samples

ADC

SAMPLES

ADDAI

Flag

Figure 7-5: ADC Interrupt Intervals with NUM_SMP

The ADDAI flag is cleared by software by writing a ‘0’, or it will be automatically cleared when a new conversion sequence

is started by setting the ADCONV bit to a ‘1’.

Note: The ADC controller processes ADC, remote diode sensors and sample and holds conversions according to the

ADC frame sequence and sets the corresponding interrupt flags in the ADST register. The user should process and clear

the interrupt flag when it is set before another flag in the ADST is set by the ADC controller. Clearing interrupts in the

upper byte of the ADST register requires multiple clock cycles. While these interrupts are being cleared, it is possible that

there is a period of up to 3 clock cycles during which an interrupt can be missed due to the time required to clear these

interrupts.

.

7.1.10

– ADC Internal Offset

The DS4830 ADC controller allows the ADC internal offset measurement. The ADC controller does not have a dedicated

buffer for the internal offset so it can only be accessed with location override enabled. For measurement of ADC internal

offset, the ADC controller connects internal ground to the ADC input and starts conversion on the ADC. Using this feature,

software can calibrate the ADC internal offset.

Refer to Application Note 5321: