Ds4830 user’s guide – Maxim Integrated DS4830 Optical Microcontroller User Manual

Page 100

DS4830 User’s Guide

100

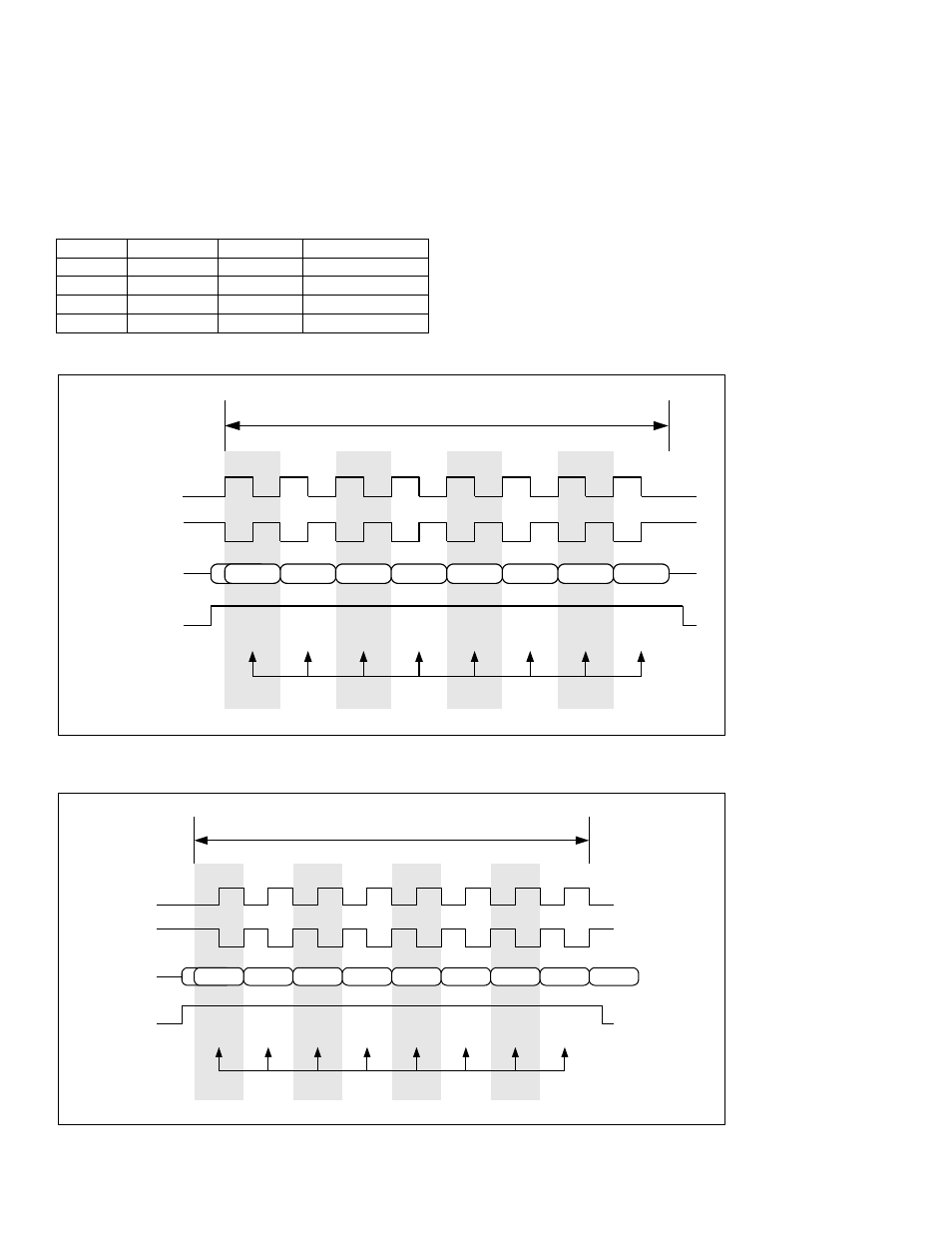

edge is used to sample the serial shift data. The Clock Phase Select (CKPHA; SPICF.1) bit controls whether the active or

inactive clock edge is used to latch the data. When CKPHA is set to 1, data is sampled on the inactive clock edge (clock

returning to the idle state). When CKPHA is set to 0, data is sampled on the active clock edge (clock transition to the

active state). Together, the CKPOL and CKPHA bits allow four possible SPI data transfer formats illustrated in Figure 12-2

and Figure 12-3. The Slave Select signal can remain asserted between successive transfers. Table 12-1 illustrates the

SPI modes.

Table 12-1 SPI Modes

CKPOL

CKPHA

Mode

Sample Point

0

0

Mode 0

Rising edge

0

1

Mode 1

Falling edge

1

0

Mode 2

Falling edge

1

1

Mode 3

Rising edge

C K P O L = 0

C K P H A = 1

C K P O L = 1

C K P H A = 1

M O S I/M IS O

SSEL

S A S = 1

S a m p lin g P o in ts

T ra n s fe r C y c le

L S B

M S B

1

2

3

4

5

6

7

8

Figure 12-2

:

SPI Transfer Formats (CKPHA=1)

CKPOL=0

CKPHA=0

CKPOL=1

CKPHA=0

MOSI/MISO

SSEL

SAS=1

Sampling Points

Transfer Cycle

LSB

MSB

1

2

3

4

5

6

7

8

MSB

MSB of

Next

Transfer

Figure 12-3

:

SPI Transfer Formats (CKPHA=0)