Section 21 – in-circuit debug mode, Section 21, In-circuit debug mode – Maxim Integrated DS4830 Optical Microcontroller User Manual

Page 155: Ds4830 user’s guide

DS4830 User’s Guide

155

SECTION 21

– IN-CIRCUIT DEBUG MODE

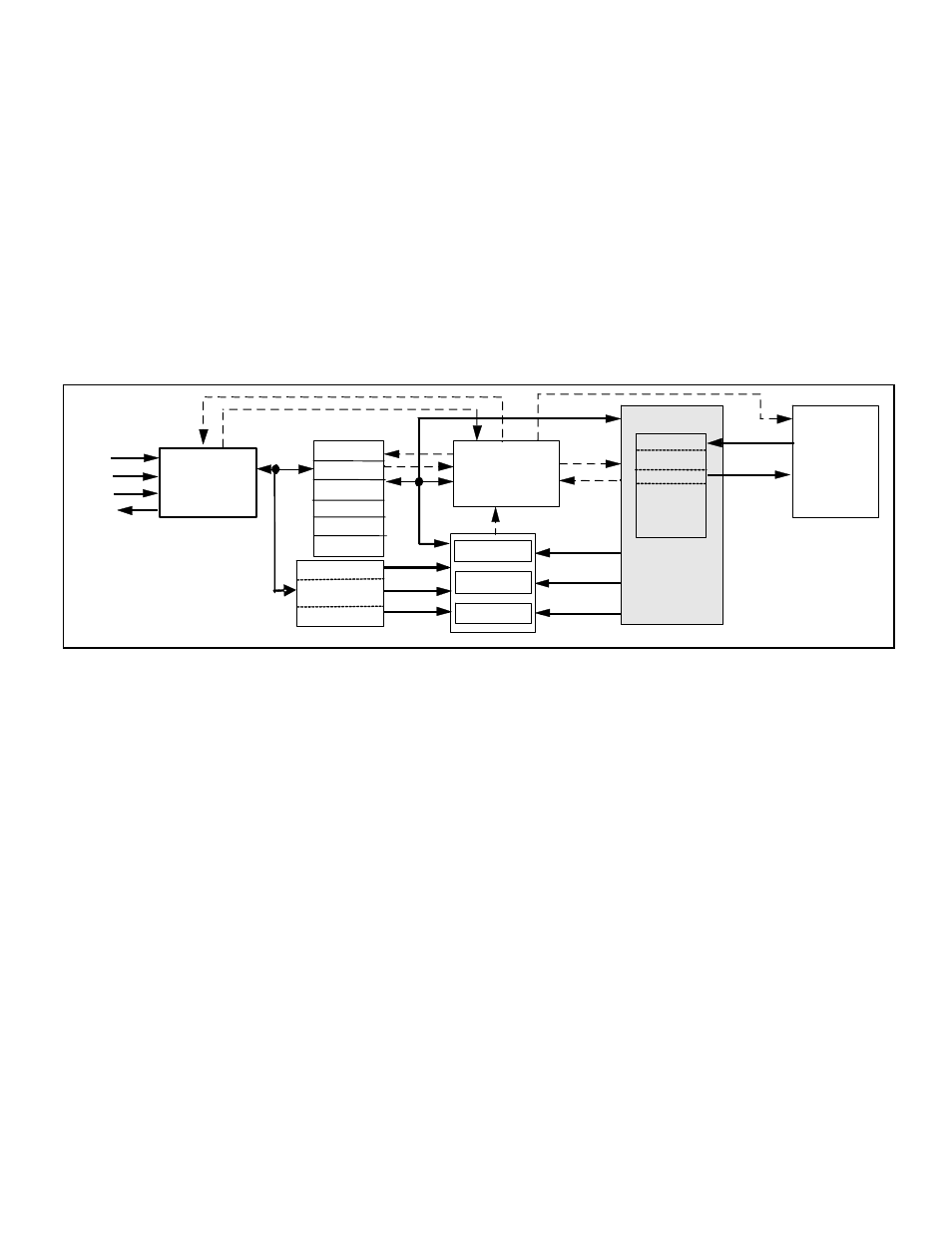

The DS4830 is equipped with embedded debug hardware and embedded ROM firmware developed for the purpose of

providing in-circuit debugging capability to the user application. The in-circuit debug mode uses the JTAG-compatible Test

Access Port (TAP) as its means of communication between the host and the DS4830. Figure 21-1 shows a block diagram

of the in-circuit debugger. The in-circuit debug hardware and software features include:

a debug engine,

a set of registers providing the ability to set breakpoints on register, code, or data,

a set of debug service routines stored in a ROM.

Collectively, these hardware and software features allow two basic modes of in-circuit debugging:

Background mode allows the host to configure and set up the in-circuit debugger while the CPU continues to

execute the normal program. Debug mode can be invoked from Background mode.

Debug mode allows the debug engine to take control of the CPU, providing read write access to internal

registers and memory, and single step trace operation.

Figure 21-1: In-Circuit Debugger

The embedded hardware debug engine is implemented as a stand-alone hardware block in the DS4830. The debug

engine can be enabled for monitoring internal activities and interacting with selected internal registers while the CPU is

executing user code. This capability allows the user to employ the embedded debug engine to debug the actual system, in

place of the in-circuit emulator that uses external hardware to duplicate operation of the microcontroller outside of the real

application environment.

To enable a communication link between the host and the microcontroller debug engine, the Debug instruction (010b)

must be loaded into the TAP instruction register using the IR-Scan sequence. Once the instruction is latched in the

instruction parallel buffer (IR2:0) and is recognized by the TAP controller in the Update-IR state, the 10-bit data shift

register is activated as the communication channel for DR-Scan sequences. The TAP instruction register retains the

Debug instruction until a new instruction is shifted via an IR-Scan or the TAP controller returns to the Test-Logic-Reset

state.

The host now can transmit and receive serial data through the 10-bit data shift register that exists between the TDI input

and TDO output during DR-Scan sequences. All background and debug mode communication (commands, data

input/output, and status) occurs via this serial channel. Each 10-bit exchange of data between the host and the DS4830

internal hardware is composed of two status bits and a single byte of command or data. The 10-bit word is always

transmitted least significant bit first with the format shown in Figure 21-2. The details of the two status bits are shown in

Table 21-1.

TMS

TDO

TDI

TCK

CPU

ROM

DEBUG

ENGINE

ICDB

ICDF

ICDC

BREAKPOINT

COMPARATOR

CODE ADDR

DATA ADDR

REG DATA

IP

IR

DATA

ADDR

ENABLE

BREAK

ICDA

ICDD

ICDTn

TAP

CONTROLLER

COMPARATOR

COMPARATOR