Maxim Integrated DS4830 Optical Microcontroller User Manual

Page 66

DS4830 User’s Guide

66

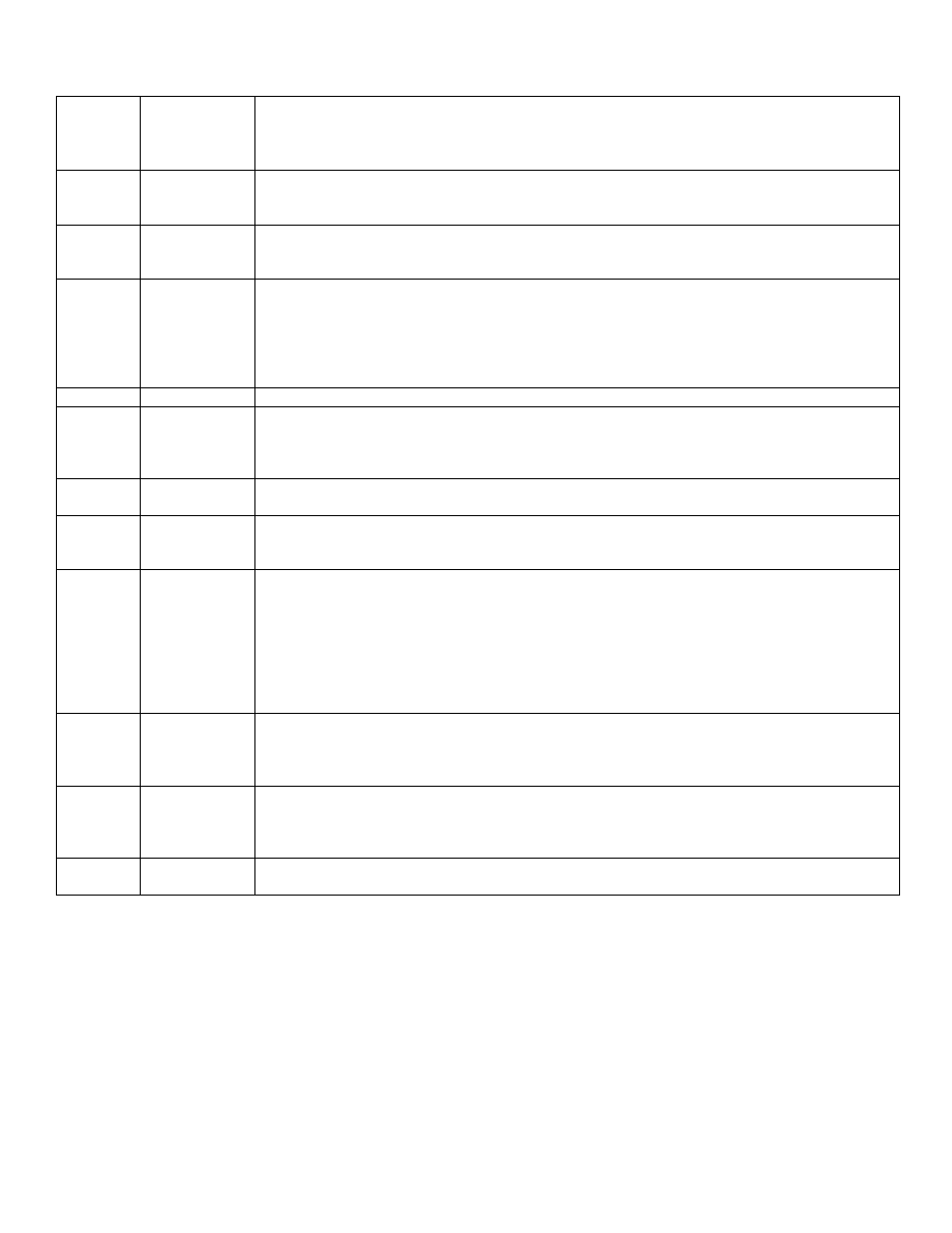

125

s. During fast mode, the sample and hold conversion priority is increased over voltage

channels in the sequence and the voltage conversions will be delayed. When this bit is ‘0’,

Sample and Hold 0 acts in the normal mode in which Sample and Hold 0 will get a

conversion slot in the ADC sequence every 250

s.

10

PIN_DIS1

Pin Discharge Enable 1.

Setting this bit to ‘1’ will enable the pin discharge function for

Sample and Hold 1. The discharge function will discharge pin capacitances (GP12-GP13)

after the Sample and Hold 1 ADC conversion.

9

PIN_DIS0

Pin Discharge Enable 0.

Setting this bit to ‘1’ will enable pin discharge function at Sample

and Hold 0. The discharge function will discharge pin capacitances (GP2-GP3) after the

Sample and Hold 0 ADC conversion.

8

SH_DUAL

Sample and Hold Dual Mode.

Setting this bit to ‘1’ will configure Sample and Hold in

“Dual Mode” operation. In dual mode, both sample and holds will act independently and will

use different sample trigger input signals. The SHEN0 (pin 23) acts as the sample trigger

input signal for Sample and Hold 0. The SHEN1 (pin 21) acts as the sample trigger input

signal for Sample and Hold 1. In single mode operation both sample and hold circuits are

triggered by the SHEN0 signal.

7

-

Reserved. The user should write 0 to this bit.

6

SH1_ALGN

Sample and Hold 1 Data Alignment Select. This bit selects the Sample and Hold 1 data

alignment mode. Setting this bit to ‘1’ returns data left aligned in ADDATA[15:2] with

ADDATA[1

:0] zero padded. Clearing this bit to ‘0’ returns data in right aligned format in

ADDATA[13:0] with ADDATA[15:14] sign-extended by ADDATA[13].

5

SHDAI1_EN

Sample and Hold 1 Interrupt Enable.

Setting this bit to ‘1’ will enable interrupt generation

on the completion of Sample and Hold 1 ADC conversion in the dual mode.

4

SMP_HLD1

Sample and Hold 1 Enable.

Setting this bit to ‘1’ enables Sample and Hold 1 operation on

GP12-GP13 input pins. The conversion results are available in ADC data buffer location

24.

3

CLK_SEL

Clock Select for Sample and Holds Trigger delayed rising edge control. This bit

selects the clock used to stop sampling when operating in SSC mode. During this mode

SSC[3:0] bits controls the delay from the start to stop of sampling..

When this bit is set to ‘0’, the peripheral clock is used for generating the SHEN pulse.

When this bit is set to ‘1’, the External Clock (CLKIN pin) is used for generating the SHEN

pulse.

See the SSC[3:0] bit description to see the effect of CLK_SEL on the SHEN0/SHEN1 pulse

generation.

2

SH0_ALGN

Sample and Hold 0 Data Alignment Select. This bit selects the Sample and Hold 0 data

alignment mode. Setting this bit to ‘1’ returns data left aligned in ADDATA[15:2] with

ADDATA[1:0] zero p

added. Clearing this bit to ‘0’ returns data in right aligned format in

ADDATA[13:0] with ADDATA[15:14] sign-extended by ADDATA[13].

1

SHDAI0_EN

Sample and Hold 0 Interrupt Enable.

Setting this bit to ‘1’ will enable interrupt generation

on the completion of Sample and Hold 0 ADC conversion when operating in dual mode

operation. In the single mode operation, this bit is set at the completion of both sample

and hold conversions.

0

SMP_HLD0

Sample and Hold 0 Enable.

Setting this bit to ‘1’ enables Sample and Hold 0 operation on

GP2-GP3 input pins. The conversion results are available in ADC data buffer location 23.