2 – fast mode operation, 3 – sampling control, Fast mode operation – Maxim Integrated DS4830 Optical Microcontroller User Manual

Page 61: Sampling control, Ds4830 user’s guide

DS4830 User’s Guide

61

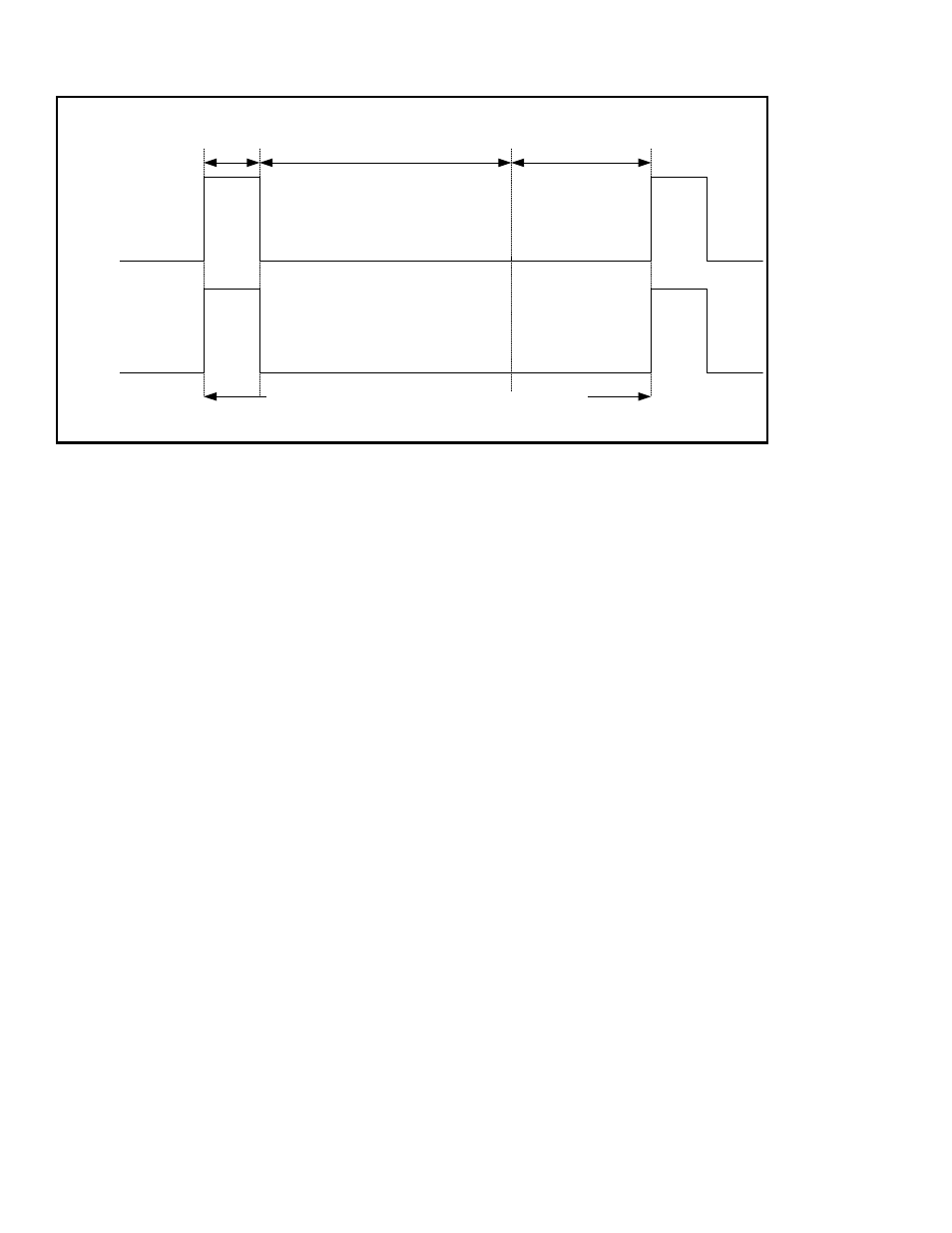

Sample Time

(min 300nSec)

Conversion Time

Depends upon ADC

Sequencing

Sample and Hold Sample and Conversion Timings

Sample Pulse

Internal or External

Min 125uSec in Fast Mode or 250uSec in Normal Mode

Pin Discharge, if

Enabled

SH Sample &

Conversion Timings

Figure 8-2

– Sample and Hold Conversion Timings

8.1.1.1

– Single Mode Operation

During the single mode operation, the SHEN signal (either internal trigger or external trigger at SHEN0) acts as a sample

pulse for both sample and hold

0 and 1. The SH0DAI bit in the ADST register is set to ‘1’, after conversion of both sample

and holds by the ADC and an interrupt is generated if enabled. The results are available at data buffer locations 23 and 24

respectively for both sample and holds after the ADC conversion is complete.

In the single mode operation the SH0DAI bit is set to ‘1’

a. At the completion of both sample and hold channels ADC conversion, if both sample and holds are enabled.

b. At the completion of only enabled sample and hold channel if any one sample and hold enabled.

The sample and hold interrupt for both sample and hold circuits can be enabled by the setting the SHDAI0_EN bit in the

SHCN register. In single mode operation, the SENR[1:0] register bits control the SHEN source for both of the sample and

holds.

8.1.1.2

– Dual Mode Operation

Dual mode operation is selected when SH_DUAL bit in the SHCN register is set to ‘1’. In this mode of operation, both the

sample and hold circuits work independently. Each sample and hold can have separate internal or external triggers. The

SHEN0 and SHEN1 provide sample pulses to Sample and Hold 0 and Sample and Hold 1 respectively for external trigger.

The Sample and Hold Internal Trigger Enable Register (SENR) has bits to enable the internal trigger for both sample and

hold circuits individually. In the dual mode operation each sample and hold generates its own Sample and Hold Data

Available Interrupt Flag (SH0DAI and SH1DAI) in the ADST register. Each of these flags can generate an interrupt if

enabled. The results are available in ADC data buffer (ADDATA, refer ADC SFR description for detail) 23 and 24

respectively.

8.1.2

– Fast Mode Operation

The DS4830 Sample and Hold provides a special “Fast Mode” feature which gives priority to a sample and hold

conversion over an ADC voltage conversion. The “Fast Mode” is enabled by setting the FAST_MODE bit to ‘1’ in the

SHCN register. This mode is useful when only Sample and Hold 0 is used. In fast mode operation the Sample and Hold 0

is guaranteed to get a conversion slot in the ADC conversion sequence every 125

s. In this mode, the user is allowed to

issue SHEN pulses (either internal of external pulse) at every 125

s interval. This bit should be used with care, as it

creates priority for the Sample and Hold0 over other sequence mode channels and hence their ADC conversion will be

delayed. When the FAST_MODE bit is set to ‘0’, the user can issue SHEN pulse every 250

s time interval.

8.1.3

– Sampling Control

The sample and hold circuitry provides the option to select the internal peripheral clock or the external clock. When the

clock select bit CLK_SEL (located in the SHCN register) is set to ‘0’, the peripheral clock is used for the sample and hold