Section 17 – supply voltage monitor (svm), Section 17, Supply voltage monitor (svm) – Maxim Integrated DS4830 Optical Microcontroller User Manual

Page 139: Ds4830 user’s guide

DS4830 User’s Guide

139

SECTION 17

– SUPPLY VOLTAGE MONITOR (SVM)

The DS4830 provides features to allow monitoring its power supply. The Supply Voltage Monitor (SVM) monitors the V

DD

power supply and can alert the processor through an interrupt if V

DD

falls below a programmable threshold.

The DS4830 provides the following power monitoring features:

SVM compares V

DD

against a programmable threshold from approximately 3.0V to 3.6V.

Optional SVM interrupt can be triggered when V

DD

drops below the programmed threshold.

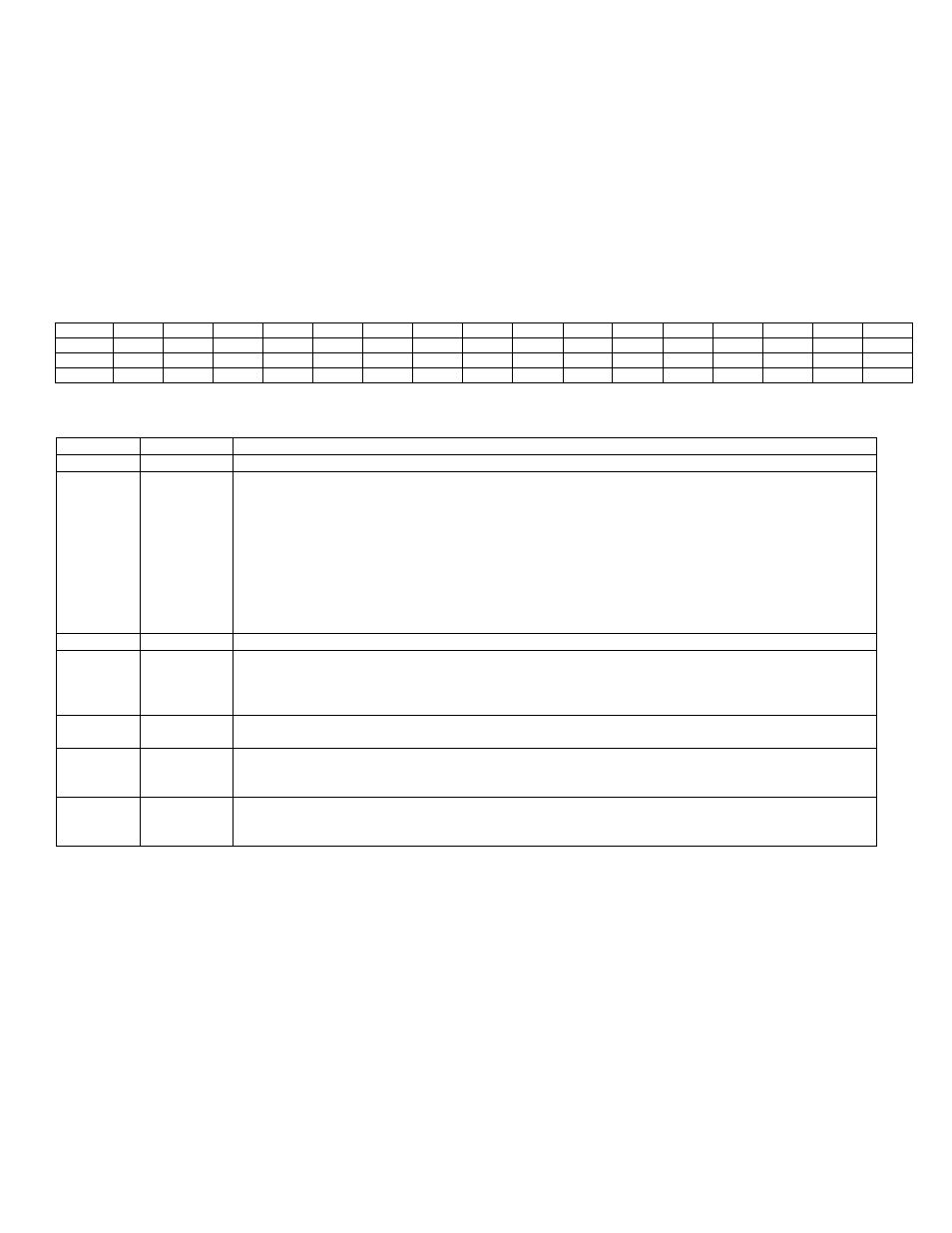

The Supply Voltage Monitor is controlled by the peripheral register SVM. This register is located in Module 1, Index 9.

Supply Voltage Monitor Register (SVM)

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

Reserved Reserved Reserved Reserved

SVTH3

SVTH2

SVTH1

SVTH0

Reserved Reserved Reserved SVMSTOP

SVMI

SVMIE

SVMRDY

SVMEN

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

r

r

r

r

rw*

rw*

rw*

rw*

r

r

r

rw

rw

rw

r

rw

*SVTH[3:0] bits can only be written when the SVM is not running (SVMEN=0)

BIT

NAME

DESCRIPTION

15:12

Reserved

Reserved. The user should write 0 to these bits.

11:8

SVTH[3:0]

Supply Voltage Threshold Bits [3:0]. These bits are used to select a user defined supply voltage

threshold. If V

DD

is below this threshold, the SVMI bit will be set and an interrupt can be generated if

enabled. The threshold level can be adjusted from 2.7V to 3.6V in 0.1V increments. The default

value is 00h (2.7V).

Supply Voltage Monitor Threshold = 2.7V + SVTH[3:0] * 0.1V

Note: that the SVTH[3:0] bits can only be modified when SVMEN = 0. Writing to these bits is ignored

if SVMEN = 1. The SVM thresholds 00h to 02h and 0Ah to 0Fh have no actual use. because these

are out of DS4830 operating V

DD

range 3.0V to 3.6V

7:4

Reserved

Reserved. The user should write 0 to these bits.

3

SVMI

Supply Voltage Monitor Interrupt. This bit is set to '1' when the V

DD

supply voltage falls below the

threshold defined by SVTH[3:0]. If SVMIE = 1, setting this bit to 1 by either hardware or software

triggers an interrupt. This bit must be cleared by software, but if V

DD

is still below the threshold, the

bit is immediately set again by hardware.

2

SVMIE

Supply Voltage Monitor Interrupt Enable. Setting this bit to 1 allows an interrupt to be generated (if

not otherwise masked) when SVMI is set to 1. Clearing this bit to 0 disables the SVM interrupt.

1

SVMRDY

Supply Voltage Monitor Ready. This read-only status bit indicates whether the SVM is ready for use.

0 = The SVM is disabled (SVMEN = 0), or the SVM is in the process of powering up.

1 = The SVM is enabled and ready for use.

0

SVMEN

Supply Voltage Monitor Enable. Setting this bit to 1 enables the SVM and begins monitoring V

DD

against the programmed (SVTH[3:0]) threshold. After SVMEN is set, SVMRDY will be set in

approximately 20 us. Clearing this bit to 0 disables the SVM.