Ds4830 user’s guide – Maxim Integrated DS4830 Optical Microcontroller User Manual

Page 54

DS4830 User’s Guide

54

7.2.3

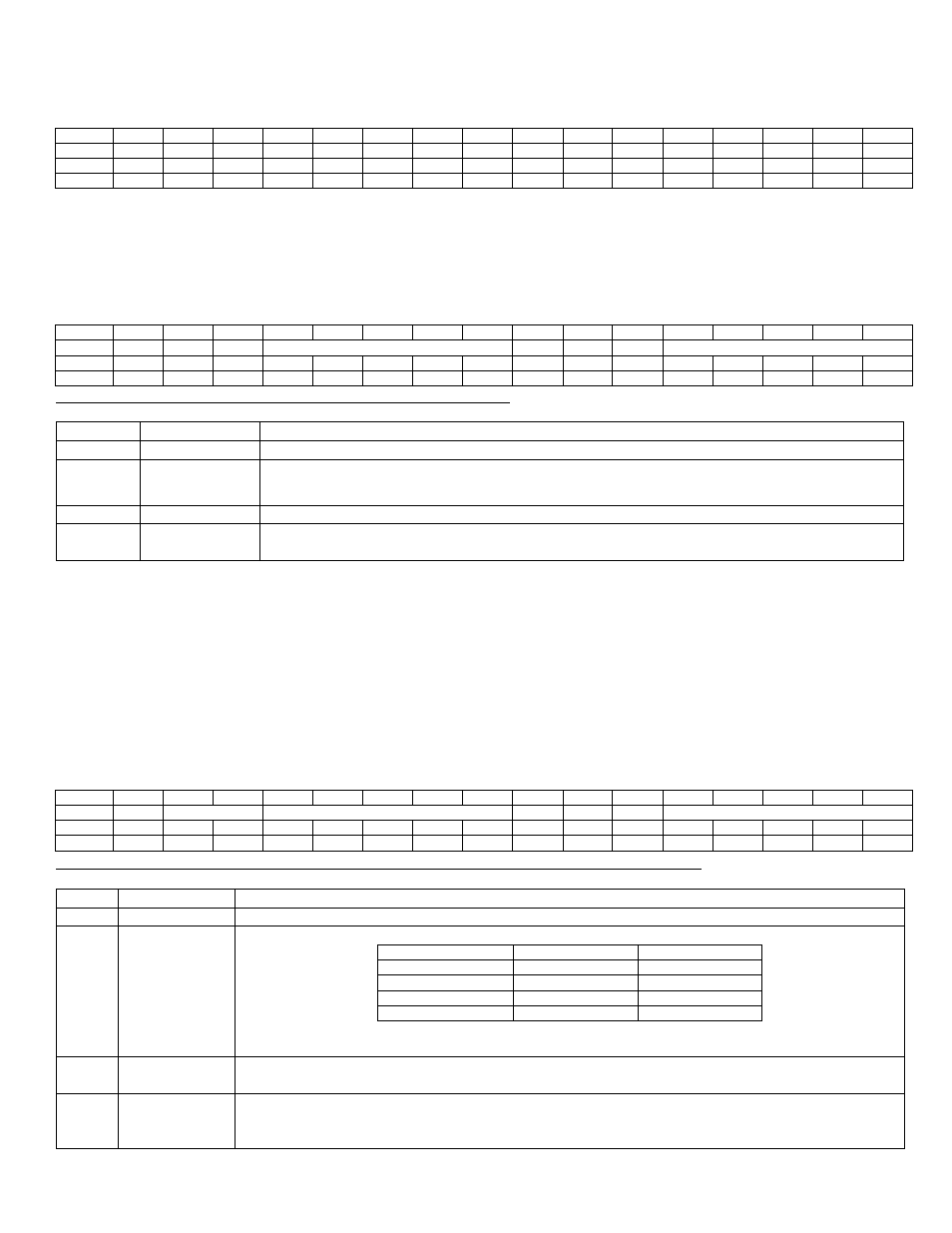

– PIN Select Register (PINSEL)

Register Address: M2 [12h]

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

PINSEL.15

PINSEL.14

PINSEL.13

PINSEL.12

PINSEL.11

PINSEL.10

PINSEL.9

PINSEL.8

PINSEL.7

PINSEL.6

PINSEL.5

PINSEL.4

PINSEL.3

PINSEL.2

PINSEL.1

PINSEL.0

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

s = special, initial value is dependent on trim settings

Each bit location in this register corresponds to the ADC input pin. When these bits are set the corresponding pins are

dedicated for ADC use. On POR, the pin selection register is 0000h which corresponds to GP0 to GP15 being GPIO, or

PWMs. For using these pins as ADC input, Sample and Hold or External Remote Diode temperature input or Quick Trip

input the corresponding PINSEL bit should be set to ‘1’.

7.2.4

– ADC Address Register (ADADDR)

Register Address: M2 [07h]

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

-

-

-

ADSTART[4:0]

-

-

-

ADEND[4:0]

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

r

r

r

rw*

rw*

rw*

rw*

rw*

r

r

r

rw*

rw*

rw*

rw*

rw*

* Unrestricted read, but can only be written to when ADCONV = 0.

BIT

NAME

DESCRIPTION

15:13

-

Reserved. The user should write 0 to these bits.

12:8

ADSTART[4:0] ADC Conversion Configuration Start Address Bits [4:0]. These bits select the first

conversion configuration register.

7:5

-

Reserved. The user should write 0 to these bits.

4:0

ADEND[4:0]

ADC Conversion Configuration Ending Address Bits [4:0]. These bits select the last

conversion configuration register. This register is inclusive when defining the sequence.

7.2.5

– ADC Data and Configuration Register (ADDATA)

Register Address: M2 [09h]

The ADDATA register is used to setup the ADC sequence configurations and also to read the results of the ADC

conversions. If the ADST.ADCFG bit is set to a 1, writing to ADDATA will write to one of the configuration registers. If

ADST.ADCFG is set to 0, reading from ADDATA will read one of the conversion results.

7.2.5.1

– ADC Configuration Register (ADDATA when ADCFG = 1)

When ADCFG = 1, writing to the ADDATA register will write to one of the configuration registers. The configuration

register written to is selected by the ADIDX[4:0] bits. The ADIDX[4:0] bits will automatically increment after a write to

ADDATA. This allows consecutive writes of ADDATA to setup consecutive configuration registers. The configuration

registers will be reset to ‘0’ on all forms of reset.

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

-

ADGAIN[1:0]

ALT_LOC[4:0]

ADACQEN ADALIGN

ADDIFF

ADCH[4:0]

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

r

rw*

rw*

rw*

rw*

rw*

rw*

rw*

rw*

rw*

rw*

rw*

rw*

rw*

rw*

rw*

* When ADCFG = 1, unrestricted read, but can only be written to when ADCONV = 0.

BIT

NAME

DESCRIPTION

15

-

Reserved. The user should write 0 to this bit.

14:13

ADGAIN[1:0]

ADC Gain Select. This bit selects the ADC scale factor.

ADGAIN[1:0]

ADC SCALE

Full Scale (typ)

00

ADCG1

1.2V

01

ADCG2

0.6V

10

ADCG3

2.4V

11

ADCG4

4.8*

* When the ADCG4 select, the ADC input should not be above 3.6V. It is limited by VDD

operating range.

12:8

ALT_LOC[4:0] Alternate location for conversion result. These bits specify the alternate location for storing

the ADC conversion result when LOC_OVR bit in the ADCN register is set to ‘1’.

7

ADACQEN

ADC Acquisition Extension Enable.

Setting this bit to ‘1’ will enable additional acquisition

time to be inserted prior to this conversion. Clearing this bit to ‘0’ will disable the extended

acquisition time.