Ds4830 user’s guide – Maxim Integrated DS4830 Optical Microcontroller User Manual

Page 161

DS4830 User’s Guide

161

(e.g., Unlock Password) require additional data from the host. Some commands need only to provide an indication of

completion to the host, while others (e.g., Read Register Map) need to supply multiple bytes of output data. To

accomplish data flow control between the host and ROM, the status bits should be used by the host to assess when the

ROM is ready for additional data and/or when the ROM is providing valid data output. Internally, the ROM can ascertain

when new data is available or when it may output the next data byte via the TXC flag. The TXC flag is an important

indicator between the debug engine and the Utility ROM debug routines. The Utility ROM firmware sets the TXC flag to 1

to indicate that valid data has been loaded to the ICDB register. The debug engine clears the TXC flag to 0 to indicate

completion of a data shift cycle, thus allowing the ROM to continue execution of a requested task that is still in progress.

The Utility ROM signals that it has completed a requested task by setting the ROM Operation Done (ROD) bit of the SC

register to logic 1. The ROD bit is reset by the debug engine when it recognizes the done condition.

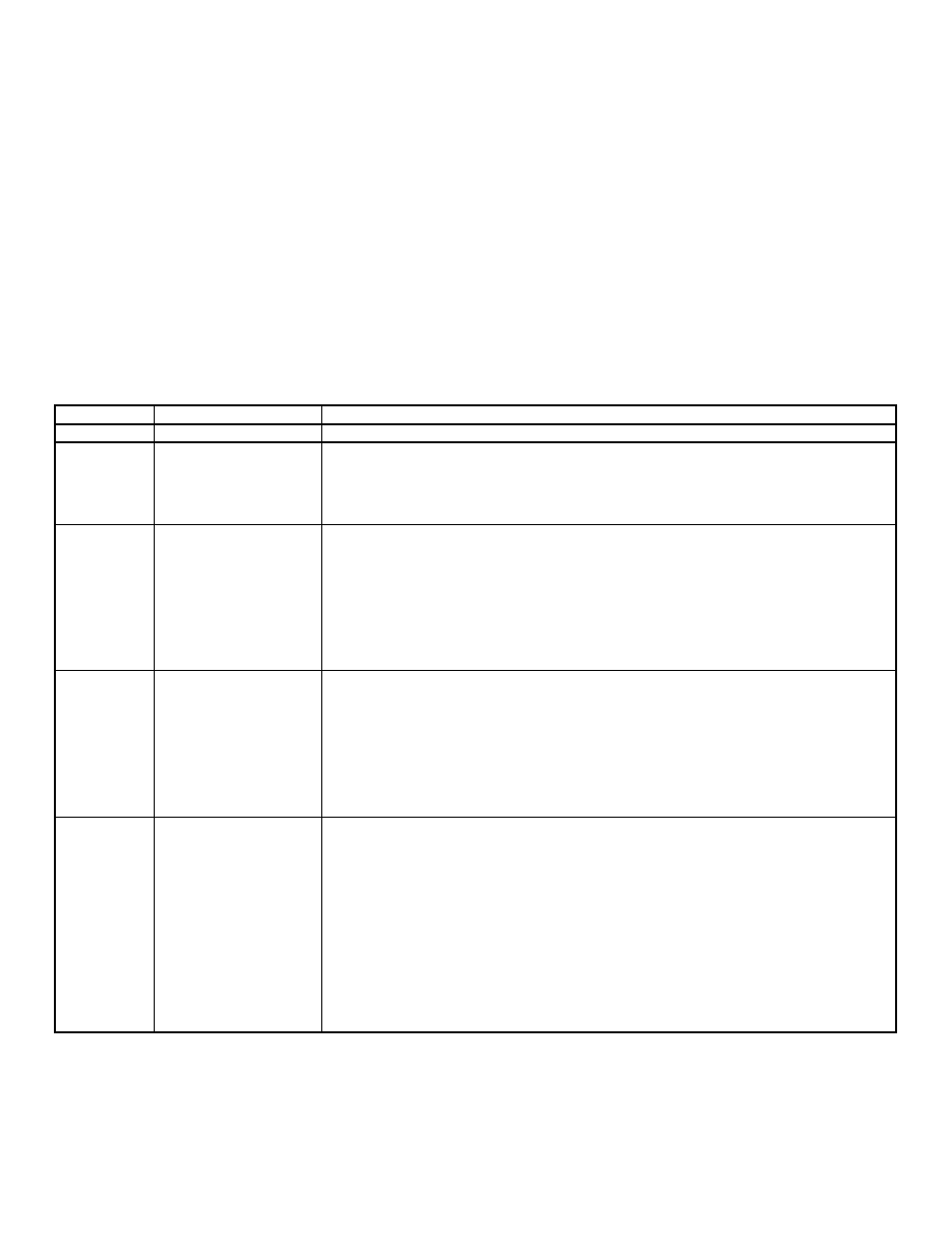

Table 21-3 shows the debug mode commands supported by the DS4830. Note that background mode commands are

supported inside debug mode, however, the documentation of these commands can be found in the Background mode

section of the document. Encodings not listed in this table are not supported in debug mode and are treated as no

operations.

Table 21-3. Debug Mode Commands

Op Code

Command

Operation

0010-0000

No Operation

No Operation.

0010-0001

Read register Map

Read data from internal registers. This command forces the debug engine to update the

CMD3:0 bits in the ICDC to 0001b and perform a jump to ROM code at x8010h. The ROM

debug service routine will load register data to ICDB for host capture/read, starting at the

lowest register location in module 0, one byte at a time in a successive order until all internal

registers are read and output to the host.

0010-0010

Read data memory

Read data from data memory. This command requires four follow-on transfer cycles, two

for the starting address and two for the word read count, starting with the LSB address and

ending with the MSB read count.

The input address must be based memory map when

executing from utility ROM, as shown in Figure 2-4.

The address is moved to the ICDA

register and the word read count is moved to the ICDD register by the debug engine. This

information is directly accessible by the ROM code. At the completion of this command

period, the debug engine updates the CMD3:0 bits to 0010b and performs a jump to ROM

code at x8010h. The ROM debug service routine will load ICDB from data memory

according to address and count information provided by the host.

0010-0011

Read program stack

Read data from program stack. This command requires four follow-on transfer cycles, two

for the starting address and two for the read count, starting with the LSB address and

ending with the MSB read count. The address is moved to the ICDA register and the read

count is moved to the ICDD register by the debug engine. This information is directly

accessible by the ROM code. At the completion of this command period, the debug engine

updates the CMD3:0 bits to 0011b and performs a jump to ROM code at x8010h. The ROM

Debug service routine will pop data out from the stack according to the information received

in the ICDA and ICDD register.

The address input is the highest value that is used, as words

are popped off the stack and returned in descending order.

0010-0100

Write register

Write data to a selected register. This command requires four follow-on transfer cycles,

two for the register address and two for the data, starting with the LSB address and ending

with the MSB data. The address is moved to the ICDA register and the data is moved to the

ICDD register by the debug engine. This information is directly accessible by the ROM code.

At the completion of this command period, the debug engine updates the CMD3:0 bits to

0100b and performs a jump to ROM code at x8010h. The ROM Debug service routine will

update the select register according to the information received in the ICDA and ICDD

registers.

Any register location can be written using this command, including reserved locations and

those used for op code support. No protection is provided by the debugging interface, and

avoiding side effects is the responsibility of the host system communicating with the

DS4830. Writing to the IP register alters the address that execution resumes from when the

debugging engine exits.