Section 5 – interrupts, Section 5, Interrupts – Maxim Integrated DS4830 Optical Microcontroller User Manual

Page 36: Ds4830 user’s guide, System module, Module 0, Module 3, Module 1, Figure 5-1: interrupt hierarchy

DS4830 User’s Guide

36

SECTION 5

– INTERRUPTS

The DS4830 provides a single, programmable interrupt vector (IV) that can be used to handle internal and external

interrupts. Interrupts can be generated from system level sources (e.g., watchdog timer) or by sources associated with the

peripheral modules. Only one interrupt can be handled at a time, and all interrupts naturally have the same priority. A

programmable interrupt mask register allows software-controlled prioritization and nesting of high-priority interrupts.

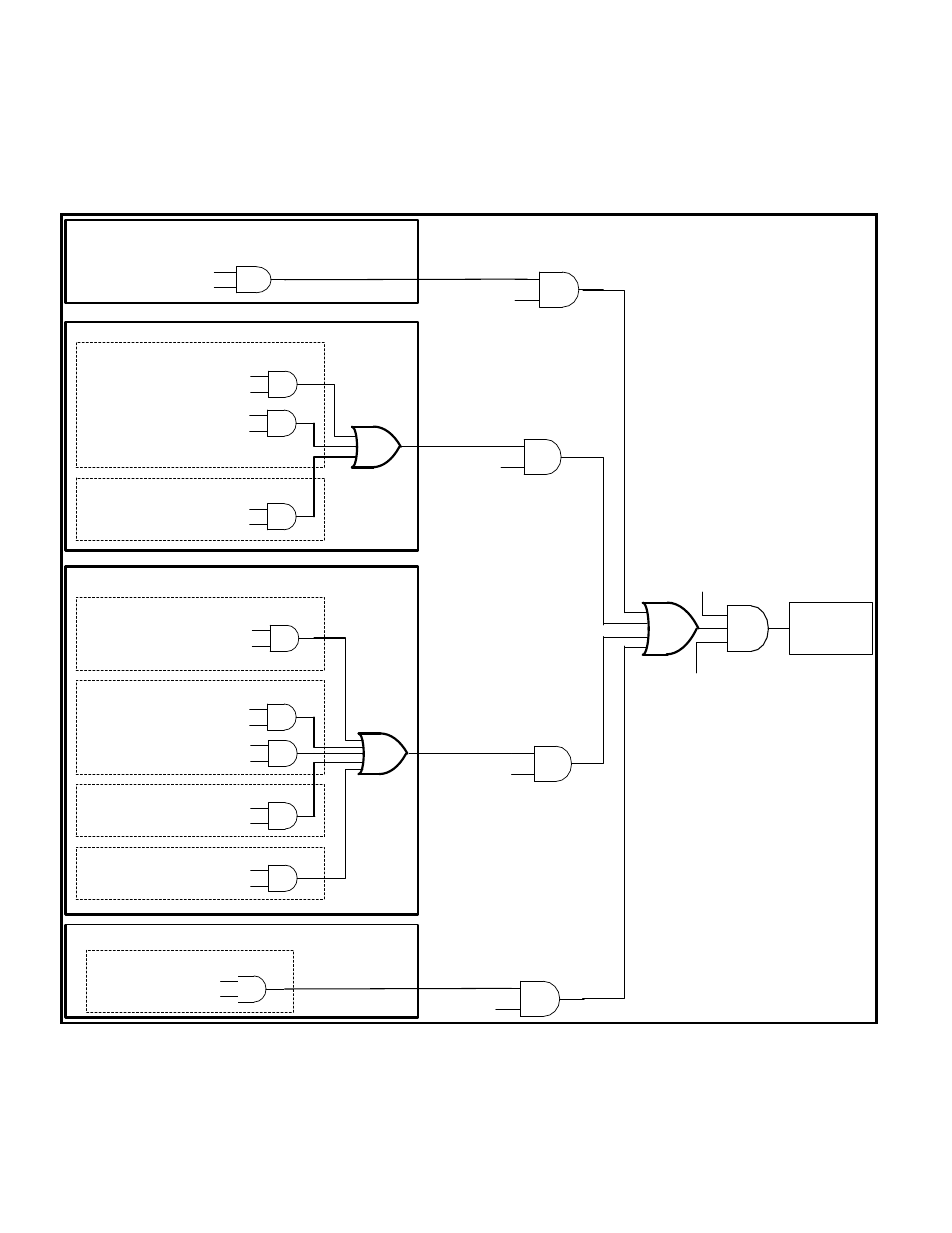

Figure 5-1 shows a diagram of the interrupt hierarchy.

System Module

WATCHDOG INTERRUPT

WDCN.WDIF

WDCN.EWDI

(local enable)

IMR.IMS

Module Enable

Module 0

GPIO INTERRUPTS

External Interrupt Pn.: EIFn.IEm

Local Enable EIEn.EXm

n can be 0,1 or 2 and m can be 0 to 7

TIMER1 INTERRUPT

Timer1 Flag GTIF

Timer Local Enable GTIE

IMR.IM0

Module0 Enable

IIR.IIS

IIR.II0

Module 3

IMR.IM3

Module3 Enable

IIR.II3

TIMER2 INTERRUPT

Timer Local Enable GTIE

External Interrupt P2.0: EIF2.IE0

Local Enable EIE2.EX0

Timer2 Flag GTIF

Module 1

External Interrupt P6.m: EIF6.IEm

Local Enable EIE6.EXm

m can be 0 to 6

PORT6 GPIO INTERRUPTS

Master I

2

C START Interrupt

I2CST_M.I2CSRI

Local Enable I2CIE_M.I2CSRIE

Any I

2

C Interrupt I2CST_M.x

Local Enable I2CIE_M.x

SVM Interrupt SVM.SVMI

Local Enable SVM.SVMIE

MASTER I

2

C INTERRUPTS

SVM INTERRUPT

Slave Interrupt SPICN_S.SPIC

Local Enable SPICF_S.ESPII

SPI Slave INTERRUPT

Module1 Enable

IIR.III1

JUMP TO

INTERRUPT

VECTOR

IC.INS

Interrupt is NOT

in Service

IC.IGE

Global Enable

IMR.IM1

Figure 5-1: Interrupt Hierarchy