Section 19 – watchdog timer, 1 - overview, 2 – watchdog timer description – Maxim Integrated DS4830 Optical Microcontroller User Manual

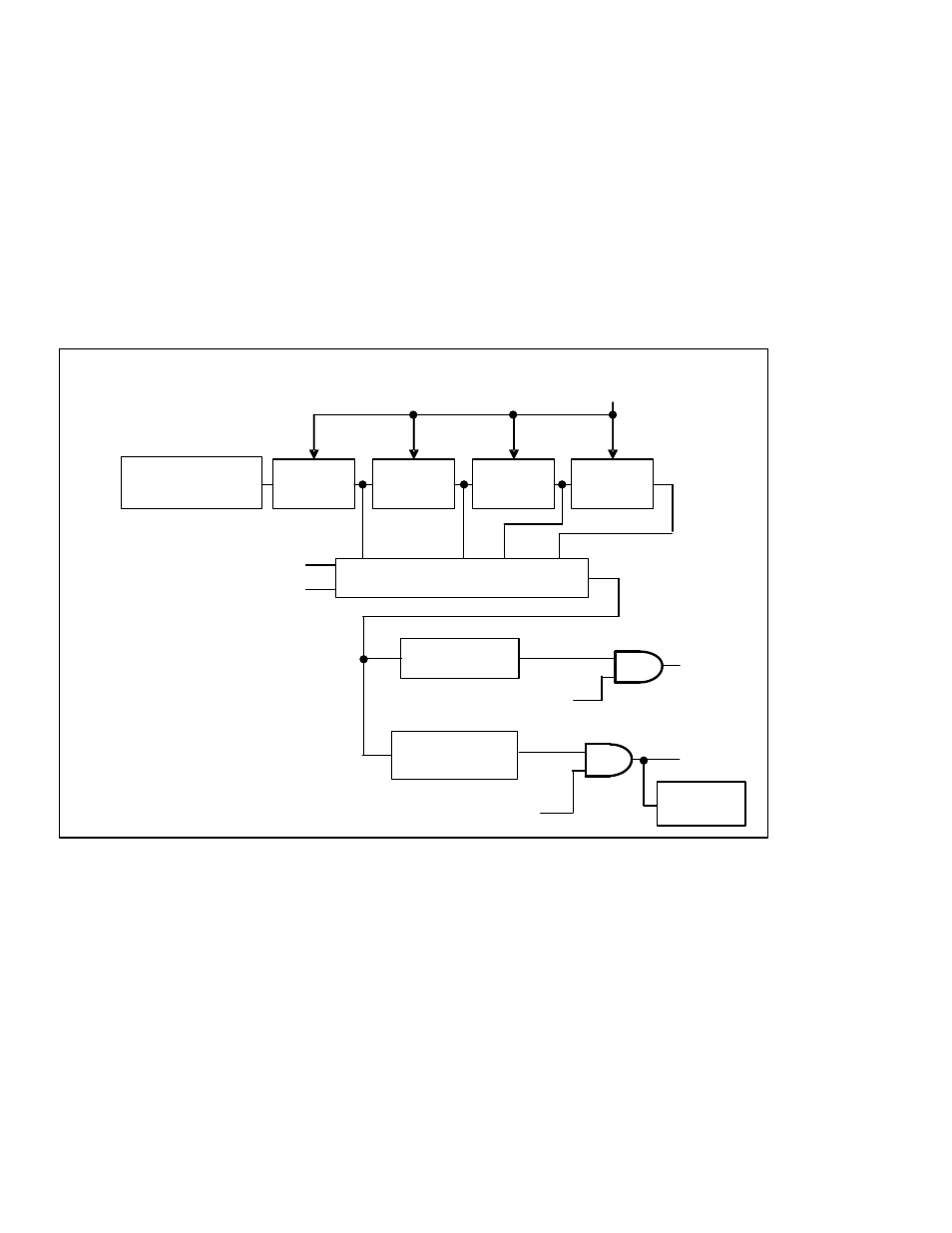

Page 146: Section 19, Watchdog timer, Watchdog timer description, Ds4830 user’s guide, Figure 19-1 : watchdog timer block diagram

DS4830 User’s Guide

146

SECTION 19

– WATCHDOG TIMER

19.1 - Overview

The Watchdog Timer is a user programmable clock counter that can serve as a time-base generator, an event timer, or a

system supervisor. As can be seen in Figure 19-1 below, the timer is driven by the main system clock and is supplied to a

series of dividers. If the watchdog interrupt and the watchdog reset are disabled (WDCN.EWDI = 0 and WDCN.EWT = 0),

the watchdog timer and its input clock are disabled. Whenever the watchdog timer is disabled, the watchdog interval timer

(per WDCN.WD[1:0] bits) and 512 clock reset counter will be reset if either the interrupt or reset function is enabled. When

the watchdog timer is initially enabled, there will be a 1-clock to 3-clock cycle delay before it starts. The divider output is

selectable, and determines the interval between timeouts. When the timeout is reached, an interrupt flag will be set, and if

enabled, an interrupt occurs. A watchdog-reset function is also provided in addition to the watchdog interrupt. The reset

and interrupt are completely discrete functions that may be acknowledged or ignored, together or separately for various

applications.

DIVIDE BY

DIVIDE BY

2

3

DIVIDE BY

2

3

DIVIDE BY

2

3

RWT

(RESET WATCHDOG)

WD1

WD0

TIMEOUT

SYSTEM CLOCK

TIMEOUT INTERVAL SELECTOR

WDIF

EWDI

(ENABLE WATCHDOG INTERRUPT)

WATCHDOG

INTERRUPT

RESET

WTRF

RESET COUNTER

512 SYSCLK DELAY

EWT

(ENABLE WATCHDOG TIMER RESET)

2

12

2

15

2

18

2

21

2

12

Figure 19-1: Watchdog Timer Block Diagram

19.2

– Watchdog Timer Description

When the watchdog timer is enabled, it begins counting system clock cycles. The watchdog count will be reset anytime

RWT is set to 1. If the watchdog count reaches the time interval set by WD1:0], a watchdog timeout occurs, setting the

Watchdog Interrupt Flag (WDCN.WDIF). A watchdog timeout will also generate an interrupt and/or reset the DS4830.

Table 19-1 describes the possible states of the watchdog timer.