4 – spi slave register descriptions, Spi slave register descriptions, Ds4830 user’s guide – Maxim Integrated DS4830 Optical Microcontroller User Manual

Page 108

DS4830 User’s Guide

108

12.5.4

– SPI Slave Register Descriptions

SPI Slave Module has four SFR registers. These are SPICN_S, SPICF_S, SPICK_S and SPIB_S. The SPI control

register SPICN_S and SPI configuration register SPICF_S controls and configures the Serial Peripheral Interface

respectively. The SPI Clock Register SPICK_S is not used in SPI Slave mode as SPI clock is driven by SPI Master. The

SPI Buffer SPIB_S is used in SPI data transfer. SPI Slave SFRs are located in Module 1.

12.5.4.1

– SPI Control Register (SPICN_S)

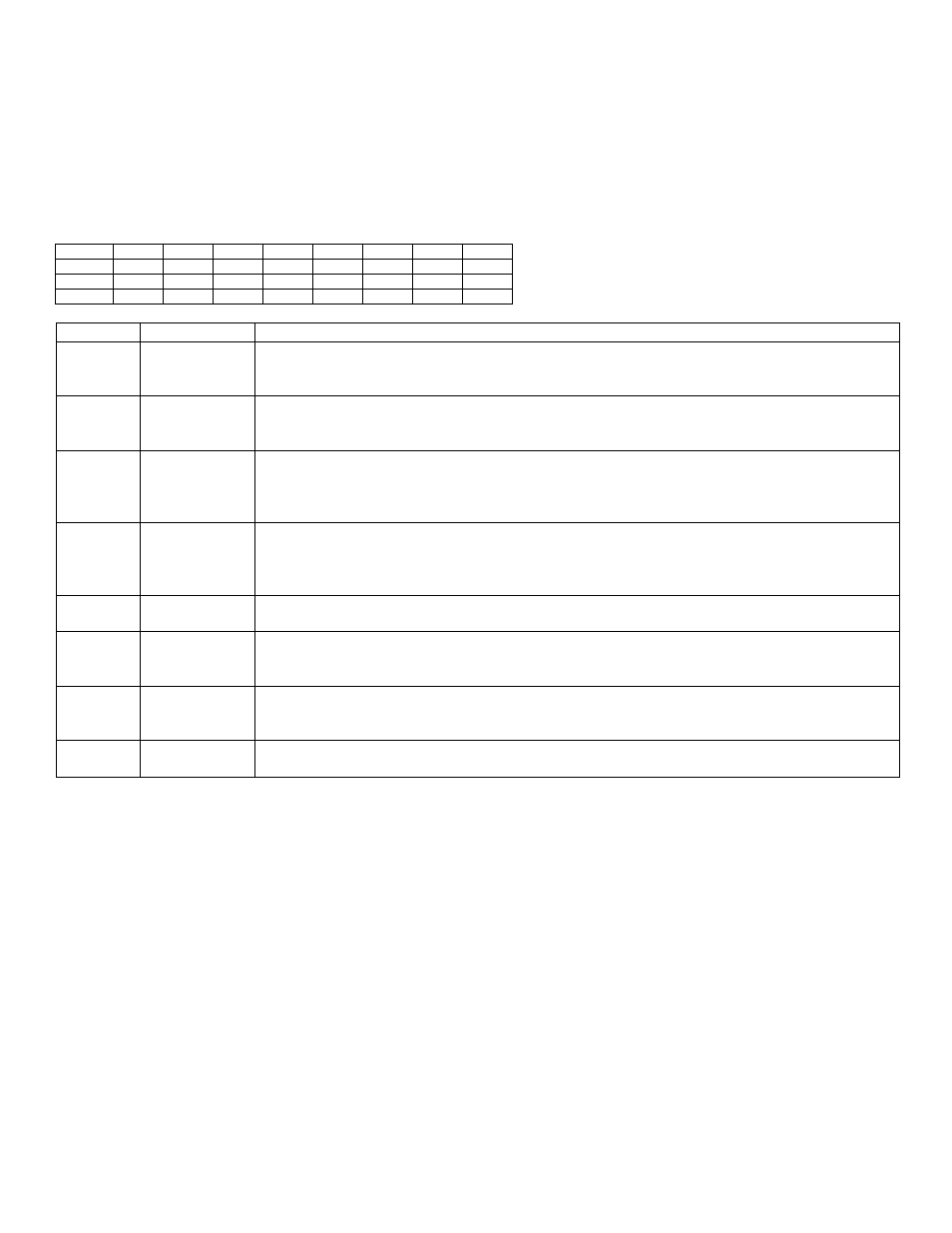

SPICN_S Register Address: M1 [12h]

Bit

7

6

5

4

3

2

1

0

Name

STBY

SPIC

ROVR

WCOL

MODF

MODFE

MSTM

SPIEN

Reset

0

0

0

0

0

0

0

0

Access

r

rw

rw

rw

rw

rw

rw

rw

BIT

NAME

DESCRIPTION

7

STBY

Write Transfer Busy Flag. This bit indicates the current status of the SPI module. STBY is

set to ‘1’ when SPI transfer cycle is started and is cleared to ‘0’ when the transfer cycle is

completed. This bit is controlled by hardware and is read only for user software.

6

SPIC

SPI Transfer Complete Flag. This bit indicates the completion of a transfer cycle when set

to ‘1’. This bit must be cleared to ‘0’ by software once set. Setting this bit to logic ‘1’ by

software will cause an interrupt if enabled.

5

ROVR

Receive Overrun Flag.

This bit indicates a receive overrun when set to ‘1’. This is caused

if two or more characters are received since the last read by the processor. The newer

data is lost.

This bit must be cleared to ‘0’ by software once set. Setting this bit to logic ‘1’

by software will cause an interrupt if enabled.

4

WCOL

Write Collision Flag.

This bit indicates a write collision when set to ‘1’. This is caused by

attempting to write to the SPIB while a transfer cycle is in progress. . This bit must be

cleared to ‘0’ by software once set. Setting this bit to logic ‘1’ by software will cause an

interrupt if enabled.

3

MODF

Mode Fault.

This flag has no meaning in slave mode.

2

MODFE

Mode Fault Enable

This flag has no meaning in slave mode. In slave mode, the SSPICS pin always functions

as a slave select input signal to the SPI module, independent of the MODFE bit.

1

MSTM

Master Mode Enable.

When set to ‘1’, SPI module will operate as Master mode when SPI

module is enabled (SPIEN = 1). When set to ‘0’, SPI module will operate as Slave mode

when SPI module enabled (SPIEN = 1).

0

SPIEN

SPI Enable.

Setting this bit to ‘1’, enables SPI Module. Setting this bit to ‘0’, disables the

SPI module.