Ds4830 user’s guide – Maxim Integrated DS4830 Optical Microcontroller User Manual

Page 53

DS4830 User’s Guide

53

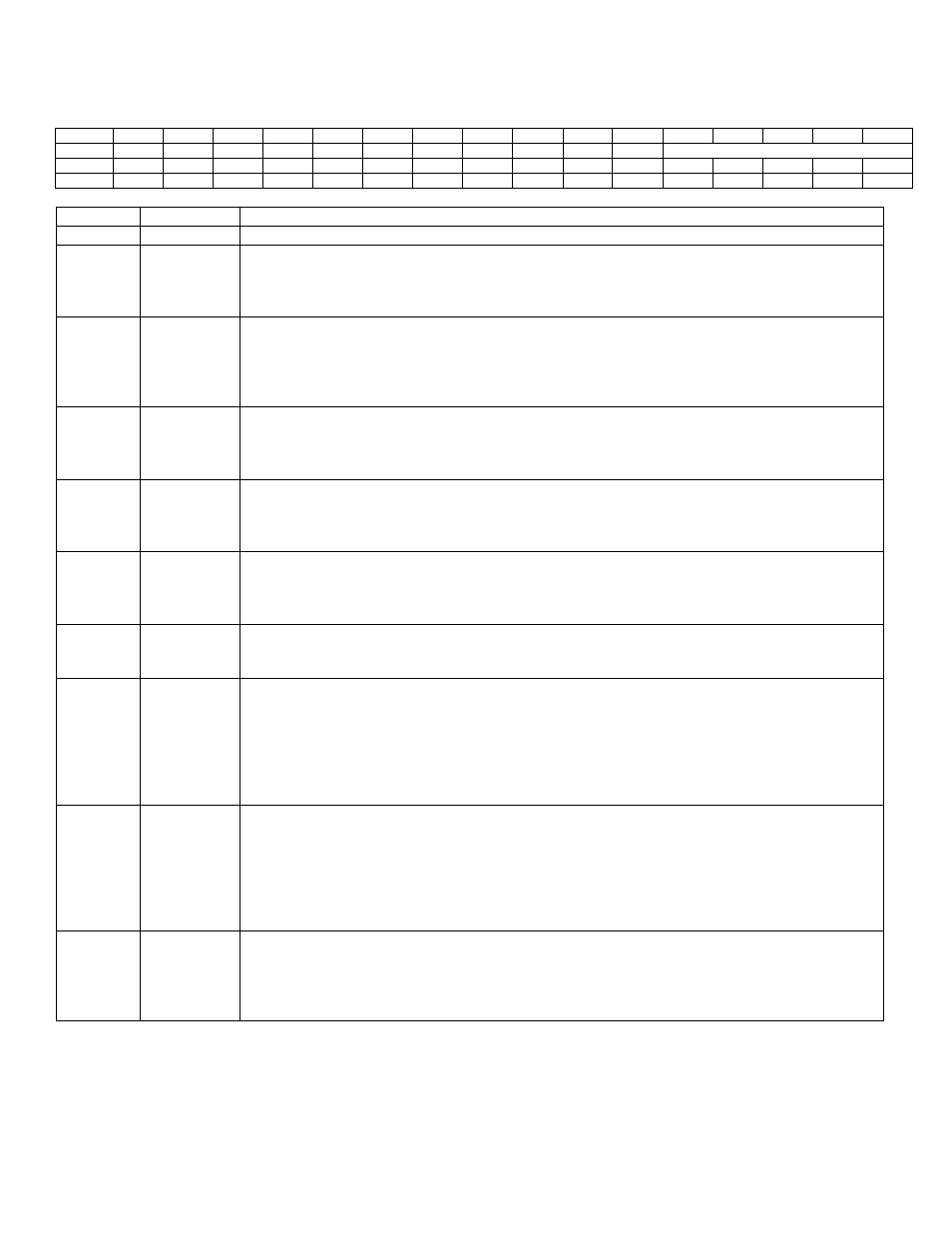

7.2.2

– ADC Status Register (ADST)

Register Address: M2[06h]

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

-

-

-

SH1DAI

SH0DAI

EX1DAI

EX0DAI

INTDAI

ADDAI

ADCONV

ADCFG

ADIDX[4:0]

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

r

r

r

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

BIT

NAME

DESCRIPTION

15:13

-

Reserved. The user should write 0 to these bits.

12

SH1DAI

Sample and Hold 1 Data Available Interrupt Flag. This bit is set to

‘1’ when Sample and

Hold is completed on GP12-GP13 in dual mode and data is ready at buffer location 24.

This flag will cause an interrupt if the

SH1DAI_EN (SHCN.5) is set to ‘1’. This bit is cleared

by software writing a ‘0’.

11

SH0DAI

Sample and Hold 0 Data Available Interrupt Flag. This bit is set to

‘1’ when Sample and

Hold is completed on GP2-GP3 if only S/H0 is used or after completion of S/H1 conversion

on GP12-GP13 when both are used in single mode. The S/H0 and S/H1 data is ready at

buffer location 23 and 24 respectively. This flag will cause an interrupt if the SH0DAI_EN

(SHCN.1) is set to ‘1’. This bit is cleared by software writing a ‘0’.

10

EX1DAI

External Temperature 1 Data Available Interrupt Flag. This bit is set to

‘1’ when an

external temperature conversion on GP10-GP11 is complete and data is ready in buffer

location 20. This flag will cause an interrupt if the EX1_IEN (TEMPCN.8) is enabled. This

bit is cleared by sof

tware writing a ‘0’.

9

EX0DAI

External Temperature 0 Data Available Interrupt Flag. This bit is set to

‘1’ when an

external temperature conversion on GP8-GP9 is complete and data is ready in buffer

location 21. This flag will cause an interrupt if the EX0_IEN (TEMPCN.9) is enabled. This

bit is cleared by software writing a ‘0’.

8

INTDAI

Internal Temperature Data Available Interrupt Flag. This bit is set to

‘1’ when an internal

temperature conversion is complete and data is ready in buffer location 22. This flag will

cause an interrupt if the INT_IEN (TEMPCN.10) is enabled. This bit is cleared by software

writing a ‘0’.

7

ADDAI

ADC Data Available Interrupt Flag. This bit is set to

‘1’ when the condition matching

ADDAINV bit is met. This flag will cause an interrupt if the ADDAIE bit is set. This bit is

cleared by software writing a ‘0’ or when software changes ADCONV bit from '0' to ‘1’.

6

ADCONV

ADC Start Conversion.

Setting this bit to ‘1’ starts the ADC conversion process. This bit

will remain set until the ADC conversion process is finished. In single sequence mode, this

bit will be cleared to ‘0’ when the ADC conversion sequence is finished. In continuous

sequence mode, this bit will remain set until the ADC conversion is stopped. To stop ADC

conversio

n at any time, write ‘0’ to this bit. The ADC will stop acquiring data after the

current conversion is finished or if the ADC is waiting during extended acquisition time, the

ADC will stop immediately.

5

ADCFG

ADC Conversion Configuration Register Select.

ADCFG = 0: The ADDATA register points to the data buffers. The ADIDX[4:0] bits

determine which data buffer is currently being accessed. When ADCFG=0, ADDATA is

read only.

ADCFG = 1: The ADDATA register points to the ADC sequence configuration registers.

The ADIDX[4:0] bits determine which configuration register is currently being accessed.

When ADCFG=1, ADDATA has read/write access.

4:0

ADIDX[4:0]

ADC Register Index Bits [4:0]. These bits together with ADCFG select the source /

destination for ADDATA access. When ADCFG=1, ADIDX [4:0] are used to address one of

24 configuration registers. When ADCFG=0, ADIDX [4:0] are used to select one of 25 data

buffers. This register value will be auto-incremented on successive access (read/write) of

ADDATA register.