Iii-4.6 flip (d flipflop (no. 65)) 109, D-flipflop 109, Flip 109 – West Control Solutions KS98-1 User Manual

Page 109: Flipflop 109, Iii-4.6 flip (d flipflop (no. 65))

III-4.6

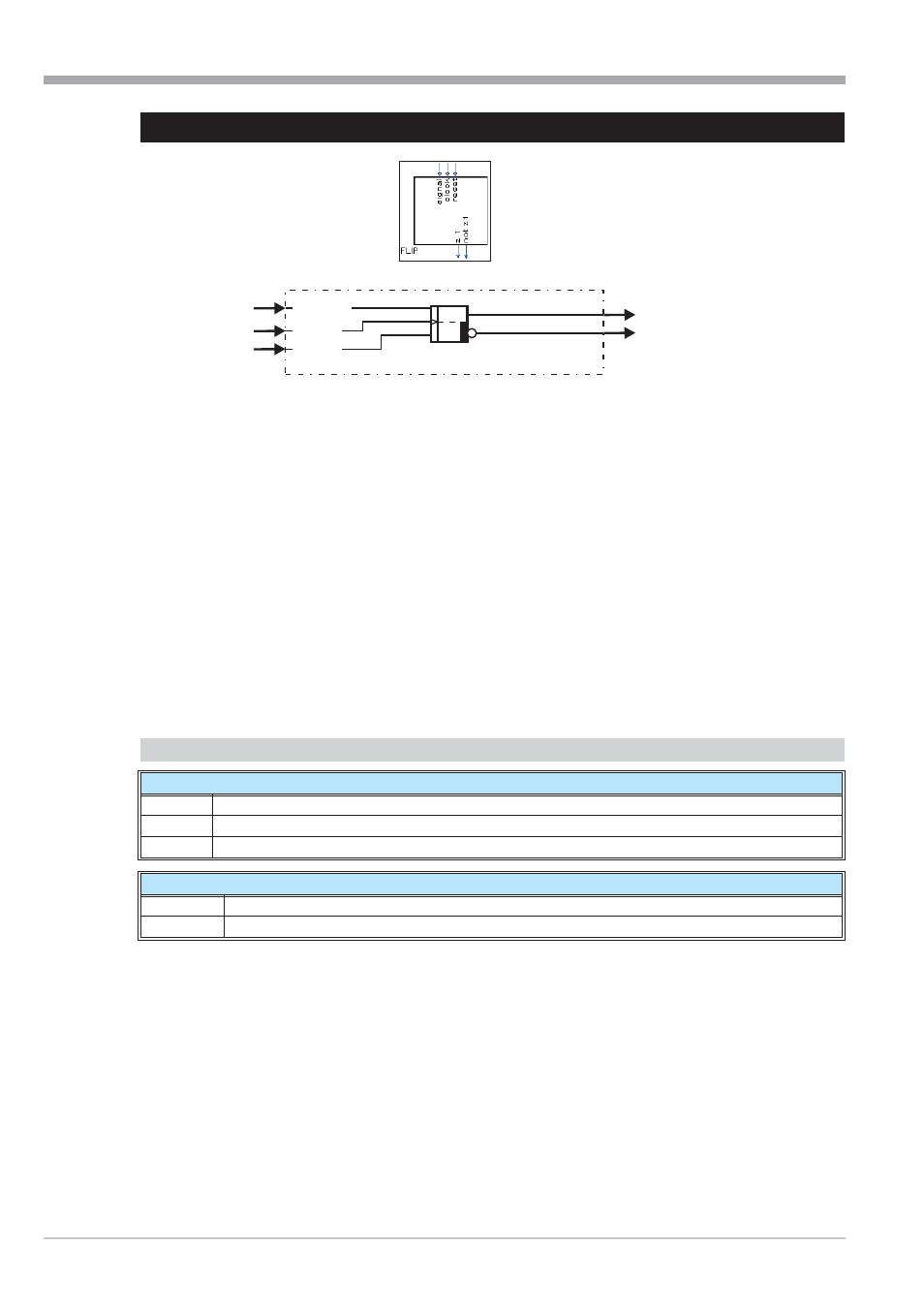

FLIP (D flipflop (No. 65))

The digital signal status at static input

signal is transferred to output z1 when

w

the signal at clock input

clock changes from 0 to 1 (positive flank), and

w

when input

reset is logic 0.

With

reset = 1, output z1 is forced to 0 independent of inputs signal and clock.

reset has priority!

Input signals

signal, clock and reset must be available at least for the duration of sampling interval T

r

se-

lected for this block (100, 200, 400 or 800ms).

In the switch-on status (initial condition),

z1 = 0! Unused inputs are interpreted as logic 0.

a

This function has a “memory”. This means: after power-on, it continues operating with the statuses at

z1

and

not z1, which existed at power-off, provided that the RAM data are still unchanged.

Inputs/outputs

Digital inputs

signal

D input - This signal is output via z1 by the positive flank (0 r 1) of

clock, when reset is not 1.

clock

Clock input - A positive flank transfers the instantaneous status at input Signal to output z1, when

reset is not 1.

reset

Reset input - sets z1 to 0

Digital outputs

z1

Flipflop output

not z1

Flipflop output NOT z1

Logic functions

9499-040-82711

III-109

FLIP (D flipflop (No. 65))

signal

clock

reset

z1

not z1