7 timer 2 reload high re, 8 timer 2 capture/compar, 9 timer 2 capture/compar – Maxim Integrated MAXQ Family User Manual

Page 97: 7 timer 2 reload high register (t2rh) -19, 8 timer 2 capture/compare register (t2c) -19, 9 timer 2 capture/compare high register (t2ch) -19, Maxq family user’s guide, 7 timer 2 reload high register (t2rh), 8 timer 2 capture/compare register (t2c), 9 timer 2 capture/compare high register (t2ch)

9-19

MAXQ Family User’s Guide

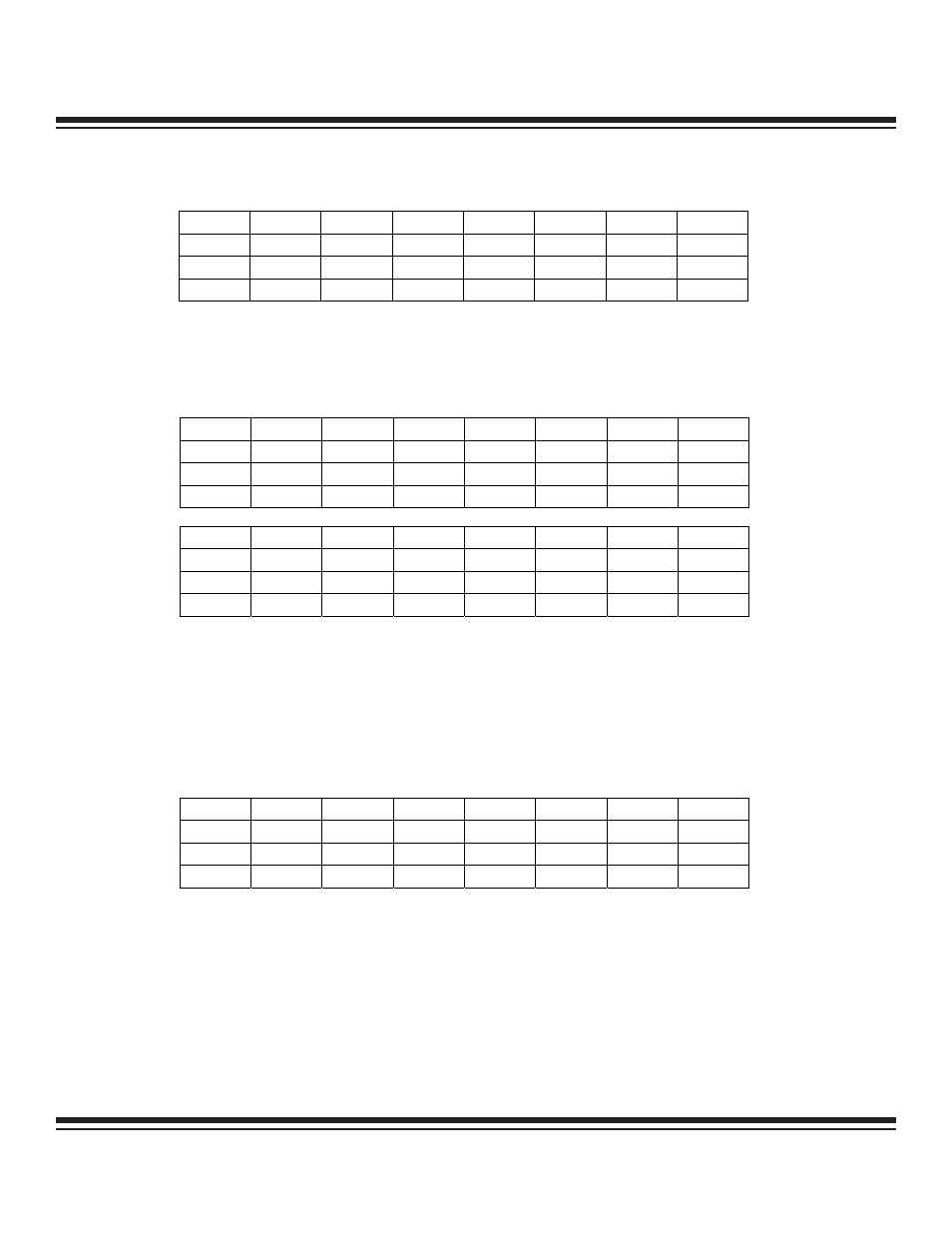

9.4.7 Timer 2 Reload High Register (T2RH)

Bits 7 to 0: Timer 2 Reload High (T2RH.[7:0]). This register is used to load and read the most significant 8-bit reload value in Timer 2.

9.4.8 Timer 2 Capture/Compare Register (T2C)

Bits 15 to 0: Timer 2 Capture/Compare (T2C.[15:0]). This 16-bit register that holds the compare value when operating in compare

mode and gets the capture value when operating in capture mode. When operating in 16-bit mode (T2MD = 0), the full 16-bits are

read/write accessible. If the dual 8-bit mode of operation is selected, the upper byte of T2C is inaccessible. T2C reads while in the

dual 8-bit mode will return 00h as the high byte and writes to the upper byte of T2C will be blocked. A separate T2CH register is pro-

vided to facilitate high-byte access.

9.4.9 Timer 2 Capture/Compare High Register (T2CH)

Bits 7 to 0: Timer 2 Capture/Compare High (T2CH.[7:0]). This register is used to load and read the most significant 8-bit capture/

compare value of Timer 2.

Bit #

7

6

5

4

3

2

1

0

Name

T2RH.7

T2RH.6

T2RH.5

T2RH.4

T2RH.3

T2RH.2

T2RH.1

T2RH.0

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

r = read, w = write

Bit #

15

14

13

12

11

10

9

8

Name

T2C.15

T2C.14

T2C.13

T2C.12

T2C.11

T2C.10

T2C.9

T2C.8

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

T2C.7

T2C.6

T2C.5

T2C.4

T2C.3

T2C.2

T2C.1

T2C.0

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

r = read, w = write

Bit #

7

6

5

4

3

2

1

0

Name

T2CH.7

T2CH.6

T2CH.5

T2CH.4

T2CH.3

T2CH.2

T2CH.1

T2CH.0

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

r = read, w = write

Maxim Integrated