4 rtc peripheral registers, 1 rtc control register, 4 rtc peripheral registers -6 – Maxim Integrated MAXQ Family User Manual

Page 147: 1 rtc control register (rcnt) -6, Maxq family user’s guide, 1 rtc control register (rcnt)

14.4 RTC Peripheral Registers

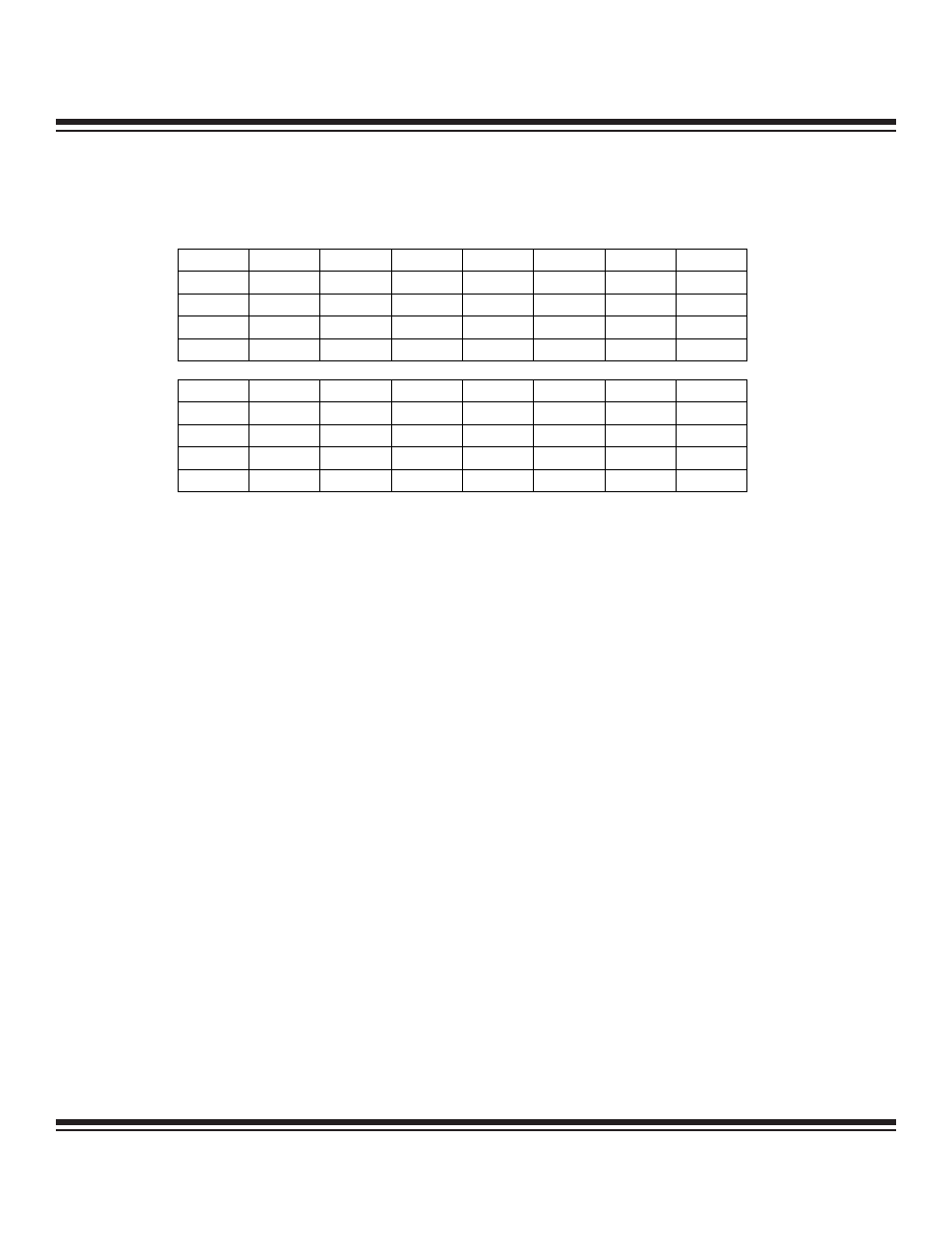

14.4.1 RTC Control Register (RCNT)

Bit 15: RTC Write Enable (WE). This register bit serves as an additional protection mechanism against unintentional writes to the RTC

enable bit (RTCE). This bit must be set to logic 1 to gain write access to the RTCE bit. When this bit is configured to logic 0, the RTCE

bit is read-only.

Bit 14: 32kHz Crystal Oscillator Disable (X32D). Setting this bit to logic 1 disables the internal oscillator circuitry connected between

the 32kHz crystal pins. In this configuration, the RTC can be driven directly by an external clock signal provided on 32KIN or CX1 pin.

Clearing this bit to logic 0 enables the internal crystal oscillator circuitry. When the internal oscillator circuitry is enabled, a warmup

delay could be required before the 32kHz oscillator begins running. The exact length of this warmup delay can vary from among

devices. Refer to the data sheet and user’s guide supplement for the specific MAXQ device for details.

Bit 13: Alternate Clock Select (ACS). This bit enables the HFClk/128 clock to drive the RTC in place of the 32kHz clock. This bit is

provided for those applications where a 32kHz clock may not be present. This bit may only be changed when RTCE = 0. When ACS

= 1, the RTC is effectively halted anytime the high-frequency oscillator is disabled (e.g., stop mode).

Bits 12, 11, 10: Reserved

Bit 9: RTC Frequency Test (FT). This register bit selects the frequency output that is possible on the SQW pin if the square-wave out-

put is enabled. Setting FT = 1 selects the 512Hz output (when SQE = 1), while FT = 0 selects the 1Hz output (when SQE = 1). This bit

has no function if the square-wave output is disabled.

Bit 8: RTC Square-Wave Output Enable (SQE). Setting this bit to logic 1 enables either the 1Hz tap or the 512Hz tap of the RTC to

the SQW pin. When cleared to 0, the SQW pin is not driven by the RTC.

Bit 7: Alarm Sub-Second Flag (ALSF). This bit is set when the subsecond timer has been reloaded by the RSSA register. Setting the

ALSF causes an interrupt request to the CPU if ASE = 1 and interrupts are enabled at the system level.

Bit 6: Alarm Time-of-Day Flag (ALDF). This bit is set when the contents of RTSH and RTSL counter registers match the 20-bit value

in the RASH and RASL alarm registers. Setting the ALDF will cause an interrupt request to the CPU if the ADE is set and interrupts are

allowed at the system level. This alarm is qualified as a stop mode wakeup source and a potential switchback function if the interrupt

has not been masked.

Bit 5: RTC Ready Enable (RDYE). Setting this bit to 1 allows a system interrupt to be generated when RDY becomes active (if inter-

rupts are enabled globally and modularly). Clearing this bit to 0 disables the RDY interrupt.

Bit 4: RTC Ready (RDY). This bit is set to 1 by hardware when the RTC count registers have updated. It can be cleared to 0 by soft-

ware at any time. It is also cleared to 0 by hardware just prior to an update of the RTC count register. This bit can generate an inter-

rupt if the RDYE bit is set to 1.

14-6

MAXQ Family User’s Guide

Bit #

15

14

13

12

11

10

9

8

Name

WE

X32D

ACS

—

—

—

FT

SQE

Power-On Reset

0

1

0

0

0

0

0

0

System Reset

0

u

u

0

0

0

0

0

Access

rw

rs

rs

r

r

r

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

ALSF

ALDF

RDYE

RDY

BUSY

ASE

ADE

RTCE

Power-On Reset

0

0

0

0

1

0

0

0

System Reset

u

u

0

0

1

u

u

u

Access

rw

rw

rw

rw

r

rw

rw

rs

r = read, w = write, s = special, u = unaffected

Maxim Integrated