7 spi peripheral registers, 1 spi control register, 7 spi peripheral registers -6 – Maxim Integrated MAXQ Family User Manual

Page 118: 1 spi control register (spicn) -6, Maxq family user’s guide, 1 spi control register (spicn)

11.7 SPI Peripheral Registers

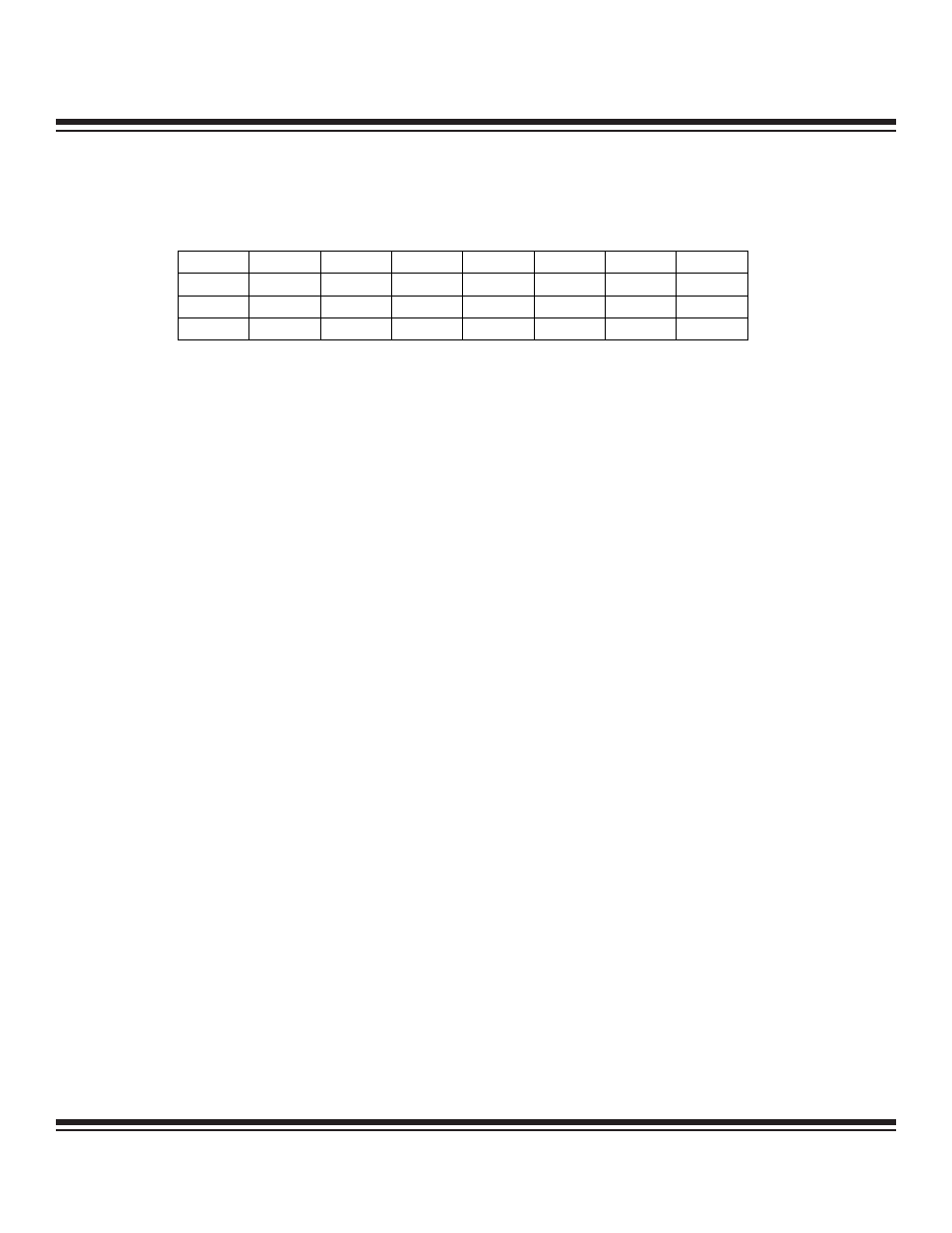

11.7.1 SPI Control Register (SPICN)

Bit 7: SPI Transfer Busy Flag (STBY). This bit is used to indicate the current transmit/receive activity of the SPI module. STBY is set

to 1 when an SPI transfer cycle starts and is cleared to 0 when the transfer cycle is completed. This bit is controlled by hardware and

is read-only for user software.

0 = SPI module is idle—no transfer in process

1 = SPI transfer in process

Bit 6: SPI Transfer Complete Flag (SPIC). This bit signals the completion of an SPI transfer cycle. This bit must be cleared to 0 by

software once set. Setting this bit to logic 1 causes an interrupt if enabled.

0 = No SPI transfers have completed since the bit was last cleared

1 = SPI transfer complete

Bit 5: Receive Overrun Flag (ROVR). This bit indicates when a receive overrun has occurred. A receive overrun results when a

received character is ready to be transferred to the SPI receive data buffer before the previous character in the data buffer is read. The

most recent receive data is lost. This bit must be cleared to 0 by software once set. Setting this bit to logic 1 causes an interrupt if

enabled.

0 = No receive overrun has occurred

1 = Receive overrun occurred

Bit 4: Write Collision Flag (WCOL). This bit signifies that an attempt was made by software to write the SPI Buffer (SPIB) while a trans-

fer was in progress (STBY = 1). Such attempts will always be blocked. This bit must be cleared to 0 by software once set. Setting this

bit to logic 1 causes an interrupt if enabled.

0 = No write collision has been detected

1 = Write collision detected

Bit 3: Mode Fault Flag (MODF). This bit is the mode fault flag for SPI master mode operation. When mode fault detection is enabled

(MODFE = 1) in master mode, detection of high-to-low transition on the SSEL pin signifies a mode fault causes MODF to be set to 1.

This bit must be cleared to 0 by software once set. Setting this bit to logic 1 causes an interrupt if enabled. This flag has no meaning

in slave mode.

0 = No mode fault has been detected

1 = Mode fault detected while operating as a master (MSTM = 1)

Bit 2: Mode Fault Enable (MODFE). When set to logic 1, the SSEL input pin is used for mode fault detection during SPI master mode

operation. When cleared to 0, the SSEL input has no function and its pin can be used for general-purposes I/O. In slave mode, the

SSEL pin always functions as a slave-select input signal to the SPI module, independent of the setting of the MODFE bit.

Bit 1: Master Mode Enable (MSTM). The MSTM bit functions as a master mode enable bit for the SPI module.

0 = SPI module operates in slave mode when enabled (SPIEN = 1)

1 = SPI module operates in master mode when enabled (SPIEN = 1)

Note that this bit can be set from 0 to 1 only when the SSEL signal is deasserted. This bit can be automatically cleared to 0 by hard-

ware if a mode fault is detected.

11-6

MAXQ Family User’s Guide

Bit #

7

6

5

4

3

2

1

0

Name

STBY

SPIC

ROVR

WCOL

MODF

MODFE

MSTM

SPIEN

Reset

0

0

0

0

0

0

0

0

Access

r

rw

rw

rw

rw

rw

rw

rw

r = read, w = write

Maxim Integrated