2 serial port mode regi, 3 serial port data buff, 4 serial port phase reg – Maxim Integrated MAXQ Family User Manual

Page 112: 2 serial port mode register (smd) -11, 3 serial port data buffer register (sbuf) -11, 4 serial port phase register (pr) -11, Maxq family user’s guide, 2 serial port mode register (smd), 3 serial port data buffer register (sbuf), 4 serial port phase register (pr)

10-11

MAXQ Family User’s Guide

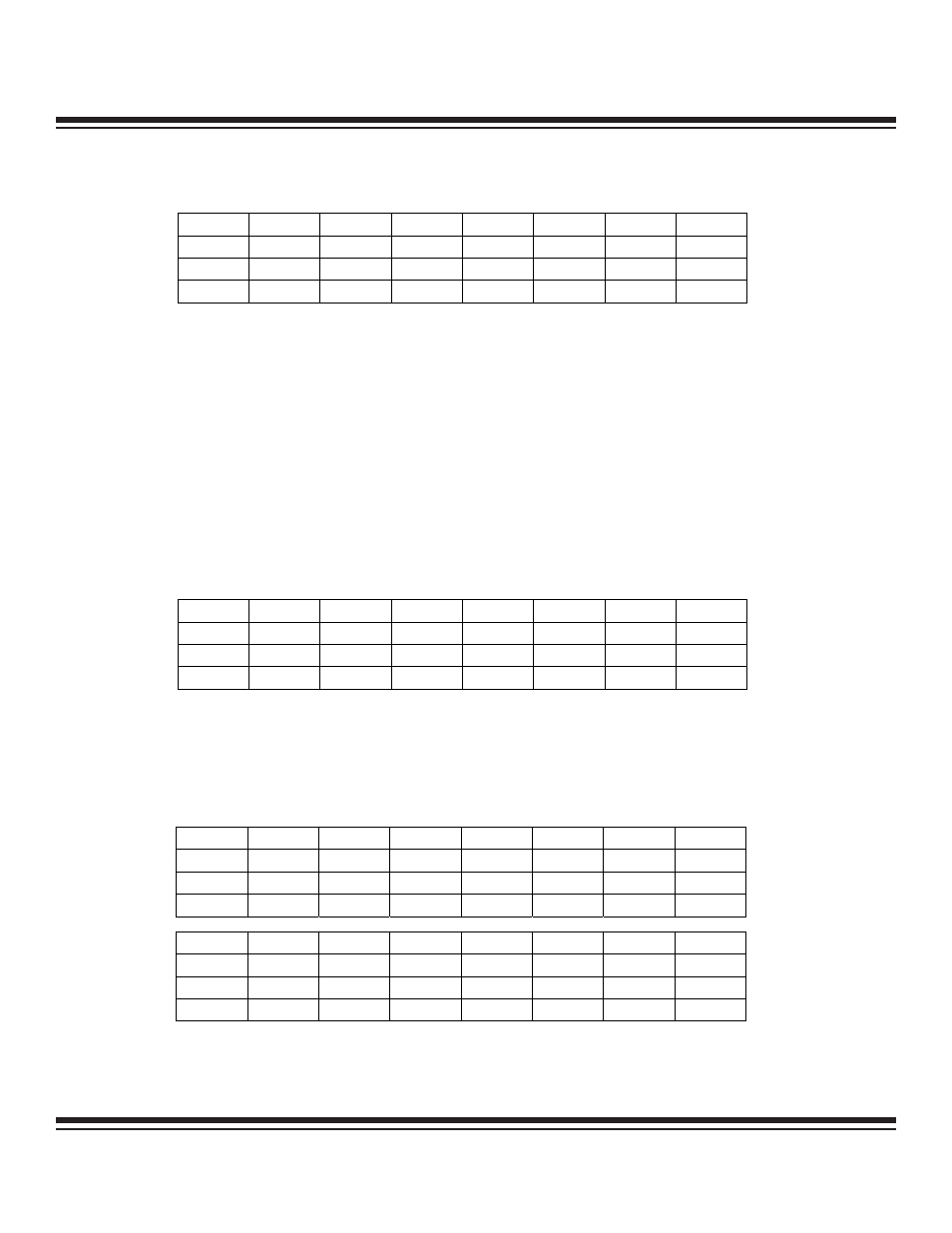

10.4.2 Serial Port Mode Register (SMD)

Bits 7 to 3: Reserved

Bit 2: Framing Error Detection Enable (FEDE). This bit selects the function of SM0 (SCON.7):

0 = SCON.7 functions as SM0 for serial port mode selection

1 = SCON.7 is converted to the Framing Error (FE) flag

Bit 1: Serial Port Baud Rate Select (SMOD). The SMOD selects the final baud rate for the asynchronous mode:

1 = 16 times the baud clock for mode 1 and 3, 32 times the system clock for mode 2

0 = 64 times the baud clock for mode 1 and 3, 64 times the system clock for mode 2

Bit 0: Enable Serial Port Interrupt (ESI). Setting this bit to 1 enables interrupt requests generated by the RI or TI flags in SCON.

Clearing this bit to 0 disables the serial port interrupt.

10.4.3 Serial Port Data Buffer Register (SBUF)

Bits 7 to 0: Serial Port Data Buffer (SBUF.[7:0]). Data for serial port is read from or written to this location. The serial transmit and

receive buffers are separate but both are addressed at this location.

10.4.4 Serial Port Phase Register (PR)

Bits 15 to 0: Serial Port Phase (PR.[15:0]). This register is used to load and read the value in the phase register.

Bit #

7

6

5

4

3

2

1

0

Name

—

—

—

—

—

ESI

SMOD

FEDE

Reset

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

rw

rw

rw

r = read, w = write

Bit #

7

6

5

4

3

2

1

0

Name

SBUF.7

SBUF.6

SBUF.5

SBUF.4

SBUF.3

SBUF.2

SBUF.1

SBUF.0

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

r = read, w = write

Bit #

15

14

13

12

11

10

9

8

Name

PR.15

PR.14

PR.13

PR.12

PR.11

PR.10

PR.9

PR.8

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

PR.7

PR.6

PR.5

PR.4

PR.3

PR.2

PR.1

PR.0

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

r = read, w = write

Maxim Integrated