3 synchronous vs. asynch, Maxq family user’s guide, 3 synchronous vs. asynchronous interrupt sources – Maxim Integrated MAXQ Family User Manual

Page 22

2-17

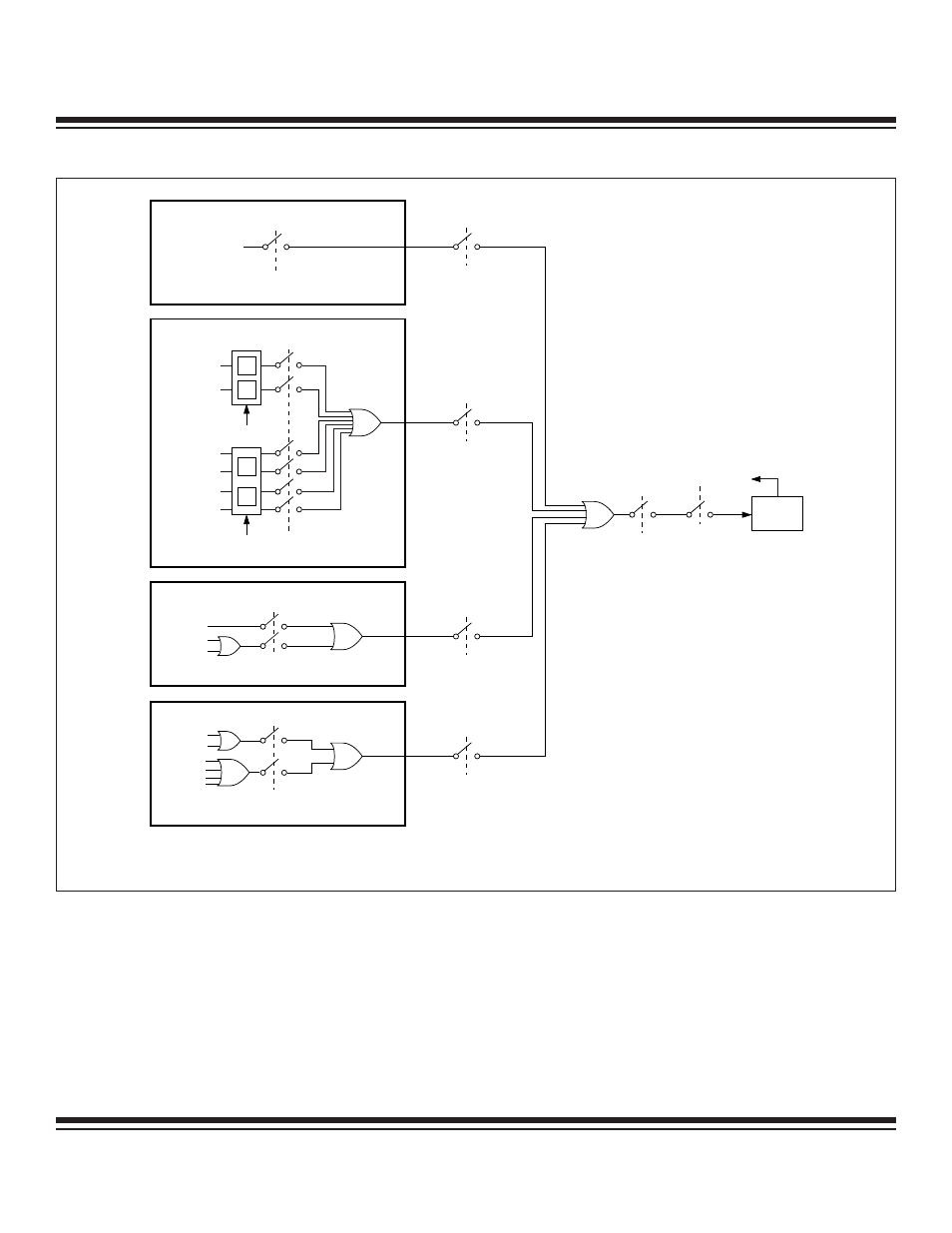

2.8.3 Synchronous vs. Asynchronous Interrupt Sources

Interrupt sources can be classified as either asynchronous or synchronous. All internal interrupts are synchronous interrupts. An internal

interrupt is directly routed to the interrupt handler that can be recognized in one cycle. All external interrupts are asynchronous interrupts

by nature. When the device is not in Stop Mode, asynchronous interrupt sources are passed through a 3-clock sampling/glitch filter cir-

cuit before being routed to the interrupt handler. The sampling/glitch filter circuit is running on the undivided source clock (i.e., before

PMME, CD1:0-controlled clock divide) such that the number of system clocks required to recognize an asynchronous interrupt request

depends upon the system clock divide ratio:

• if the system clock divide ratio is 1, the interrupt request is recognized after 3 system clock;

SYSTEM MODULES

WATCHDOG

EWDI

(LOCAL ENABLE)

TIMER/COUNTER MODULE

TF0

TF1

EXF1

SPIC

MODF

ET0, ET1

(LOCAL ENABLES)

IMx

(MODULE ENABLE)

GPI/O MODULE

INT0

EX0-EX5

(LOCAL ENABLES)

IT0

INT1

INT2

INT3

IT1

INT4

INT5

IMx

(MODULE ENABLE)

IMS

(SYSTEM ENABLE)

SERIAL I/O MODULE

RI

TI

ESI, ESPII

(LOCAL ENABLES)

IMx

(MODULE ENABLE)

ROVR

WCOL

IGE

(GLOBAL ENABLE)

NOTE: ONLY A FEW OF THE MANY POSSIBLE MAXQ PERIPHERAL MODULES ARE SHOWN IN THIS INTERRUPT

HIERARCHY FIGURE. PLEASE REFERENCE THE CORRESPONDING DATA SHEET FOR INTERRUPT FLAG

AND ENABLE BITS SPECIFIC TO A GIVEN DEVICE.

INS

(INTERRUPT IN SERVICE)

INTERRUPT

VECTOR

ƒ

ƒ

ƒ

ƒ

Figure 2-10. MAXQ Interrupt Source Hierarchy Example

MAXQ Family User’s Guide

Maxim Integrated