6 ir peripheral register, 1 infrared control regis, 6 ir peripheral register -23 – Maxim Integrated MAXQ Family User Manual

Page 101: 1 infrared control register (ircn) -23, Figure 9-14. bit length decoding example -23, Maxq family user’s guide, 1 infrared control register (ircn)

9-23

MAXQ Family User’s Guide

9.6 IR Peripheral Register

9.6.1 Infrared Control Register (IRCN)

Bits 7 to 3: Reserved

Bit 2: Infrared Subcarrier Enable (IREN). This register bit enables a special mode of operation for Timer 2. To use the IR hardware

(i.e., before setting IREN = 1), Timer 2 should be configured properly to the dual 8-bit timer/8-bit counter mode. Setting IREN = 1

enables the IRRX mode if IRTX = 0, and enables the IRTX mode if IRTX = 1. In both cases, the T2L 8-bit timer output is fed as input to

the T2H 8-bit counter.

Bit 1: Infrared Transmit Enable (IRTX). This register bit controls the contextual usage of the IRBB bit. When IRTX = 0, the IRBB bit

captures the T2P(IRRX) pin state on compare matches. When IRTX = 1, the IRBB enables the T2L subcarrier output to the T2PB out-

put pin on the next T2H counter overflow. This bit has no effect when IREN = 0.

Bit 0: Infrared Bit Bang Bit (IRBB). This register bit serves different purposes depending upon whether the IR Transmit Enable is con-

figured as a 1 or 0. When IRTX = 1, the IR transmit mode is in effect and setting the IRBB bit to logic 1 enables the T2POL[1] modified

T2L output starting at the next T2H counter overflow (allowing the subcarrier to be output to the pin). The user software is responsible

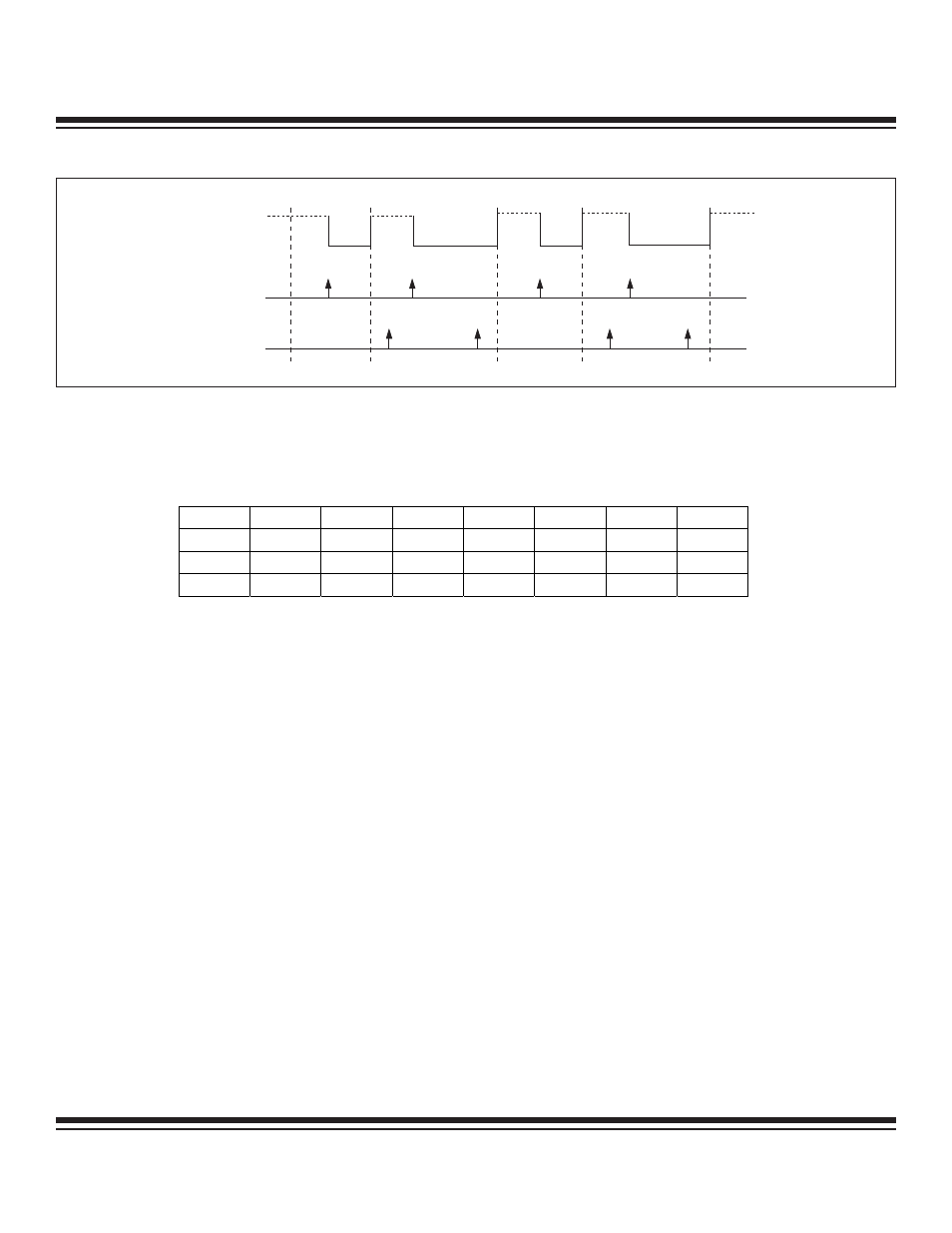

for manually toggling IRBB and controlling the T2RH reload to achieve the desired protocol. For receive mode, IRTX = 0, the IRBB bit

contains the latched state of the IRRX pin each time that a compare match (with T2CH) occurs. The user software is responsible for

unloading IRBB and translating the recorded bit stream into the proper IR serial receive data.

T2P INPUT

0

0

1

1

RELOAD (FALLING)

CCF[1:0] = 10b

IRBB BIT

(T2CH MATCH)

Figure 9-14. Bit Length Decoding Example

Bit #

7

6

5

4

3

2

1

0

Name

—

—

—

—

—

IREN

IRTX

IRBB

Reset

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

rw

rw

rw

r = read, w = write

Maxim Integrated